US009954427B2

# (12) United States Patent

#### Venkataramanan et al.

# (10) Patent No.: US 9,954,427 B2

# (45) **Date of Patent:** Apr. 24, 2018

# (54) CONVERTER CONTROL USING REDUCED LINK CAPACITOR

(71) Applicant: Wisconsin Alumni Research Foundation, Madison, WI (US)

(72) Inventors: Venkata Giri Venkataramanan,

Madison, WI (US); Mahima Gupta,

Madison, WI (US)

(73) Assignee: Wisconsin Alumni Research

Foundation, Madison, WI (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 14/934,337

(22) Filed: Nov. 6, 2015

### (65) Prior Publication Data

US 2017/0133922 A1 May 11, 2017

(51) Int. Cl. H02M 7/53862 (2007.01) H02M 1/14 (2006.01) H02M 7/797 (2006.01) H02M 7/5387 (2007.01)

(52) **U.S. Cl.** CPC ...... *H02M 1/143* (2013.01); *H02M 7/797* (2013.01)

#### (58) Field of Classification Search

CPC ............ H02M 7/42; H02M 7/53; H02M 7/537; H02M 7/53846; H02M 7/53862; H02M 7/5387; H02M 7/53871; H02M 7/53873; H02M 7/53875; H02M 7/5395

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 4,677,539 A *  | 6/1987 | Erickson H02M 7/5387 |  |  |  |  |

|----------------|--------|----------------------|--|--|--|--|

|                |        | 363/132              |  |  |  |  |

| 6,879,062 B2 * | 4/2005 | Oates H02J 3/00      |  |  |  |  |

|                |        | 307/106              |  |  |  |  |

| 7,102,903 B2*  | 9/2006 | Nakamura H02P 27/08  |  |  |  |  |

|                |        | 318/139              |  |  |  |  |

| 7,164,254 B2   | 1/2007 | Kerkman et al.       |  |  |  |  |

| 7,593,243 B2   | 9/2009 | Ganev et al.         |  |  |  |  |

| 7,738,267 B1   | 6/2010 | Tallam et al.        |  |  |  |  |

| 8,649,195 B2   | 2/2014 | Mao et al.           |  |  |  |  |

| (Continued)    |        |                      |  |  |  |  |

#### OTHER PUBLICATIONS

Van Der Broeck et al., Analysis and Realization of a Pulsewidth Modulator Based on Voltage Space Vectors, IEEE Transactions on Industry Applications, vol. 24. No. 1, 1988, pp. 142-150.

(Continued)

Primary Examiner — Gary L Laxton (74) Attorney, Agent, or Firm — Bell & Manning, LLC

### (57) ABSTRACT

A controller selects a first switch vector based on a current, voltage, or power of a multi-phase load or power source. The first switch vector identifies a first state for each of a plurality of half-bridges of a converter as on or as off during a first interval. A second switch vector is selected based on the current, voltage, or power of the multi-phase load or power source. The second switch vector identifies a second state for each of the half-bridges as on or as off during a second interval. The first interval is computed based on the selected first switch vector. The second interval is computed based on the selected second switch vector. Each of the plurality of half-bridges is controlled as on or as off during the first interval based on the selected first switch vector and during the second interval based on the selected second switch vector.

### 20 Claims, 33 Drawing Sheets

## (56) References Cited

## U.S. PATENT DOCUMENTS

| 8,842,454    | B2  | 9/2014  | Johnson et al.          |

|--------------|-----|---------|-------------------------|

| 8,898,025    | B2  | 11/2014 | Yin et al.              |

| 2004/0047166 | A1  |         | Lopez-Santillana et al. |

| 2010/0090533 | A1* | 4/2010  | Shimada B60L 11/1811    |

|              |     |         | 307/66                  |

| 2010/0259955 | A1* | 10/2010 | Shimada H02M 7/219      |

|              |     |         | 363/49                  |

| 2015/0188453 | A1* | 7/2015  | Damson H02M 7/53875     |

|              |     |         | 318/504                 |

| 2017/0063248 | A1  | 3/2017  | Lee et al.              |

|              |     |         |                         |

### OTHER PUBLICATIONS

Gupta et al., Quantum Modulated Voltage Source Converters with Minimal DC Bus Capacitance, WEMPEC 34th Annual Review Meeting, May 20, 2015.

Meeting, May 20, 2015.

Gupta et al., Three Phase Voltage Source Inverters with Only Decoupling Capacitors on the DC Bus, WEMPEC 34th Annual Review Meeting, May 20, 2015.

<sup>\*</sup> cited by examiner

Fig. 7

Fig. 10

Fig. 12

Fig. 18

Fig. 19

Fig. 20

Apr. 24, 2018

Fig. 24

Fig. 25

Fig. 26a

-ig. 26t

Fig. 27

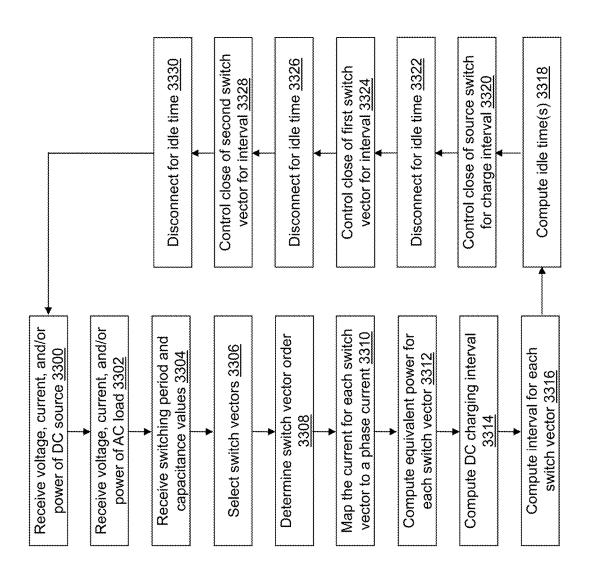

Fig. 32

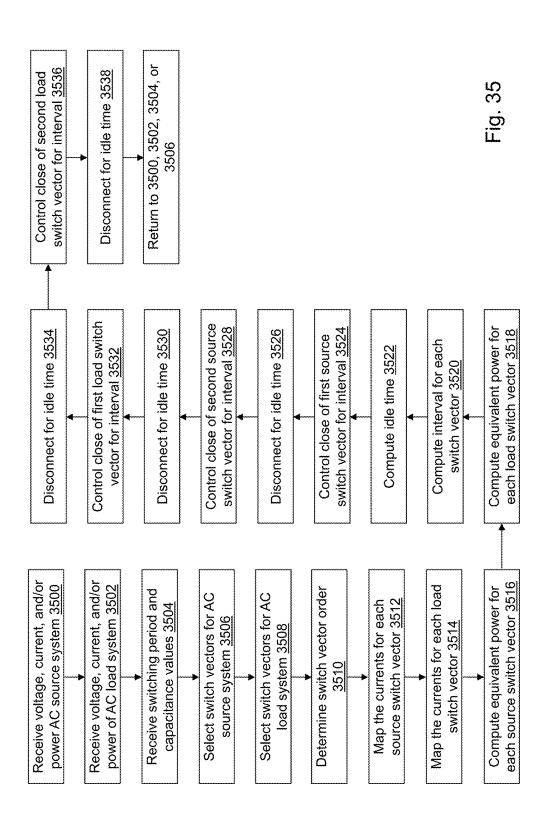

Fig. 33

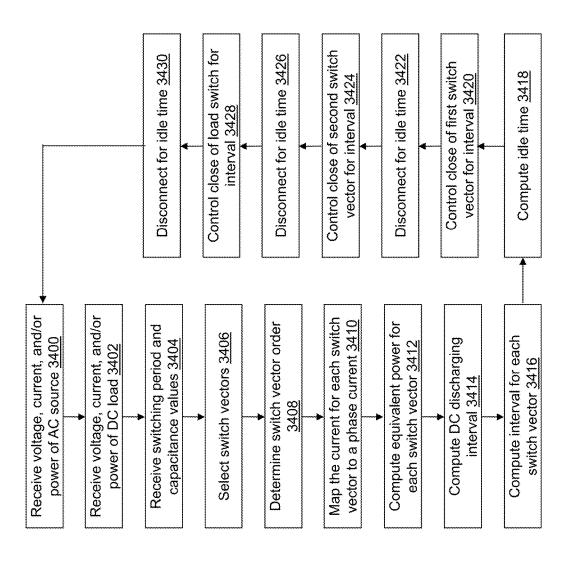

Fig. 34

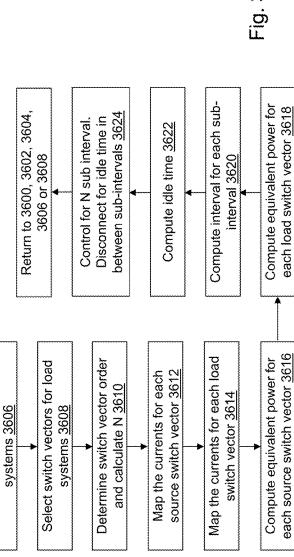

Receive voltage, current, and/or

power of all DC and AC source

systems 3600

Receive voltage, current, and/or

power of all DC and AC load

systems 3602

Select switch vectors for source

Receive switching period and

capacitance values 3604

# CONVERTER CONTROL USING REDUCED LINK CAPACITOR

#### BACKGROUND

A power converter is an electrical device for converting electrical energy from one form to another, such as between alternating current (AC) and direct current (DC), between different voltages or frequencies, or a combination of these. Three-phase electric power requires the use of power converters to control the flow of electric energy by supplying voltages and currents in a form that is optimally suited for the load. Conventional three-phase alternating current (AC) converter topologies use an intermediate capacitive direct 15 current (DC) link. To synthesize a sinusoidal output, sinusoidal pulse width modulation is typically used, and a stiff voltage is maintained across the capacitive DC link, which means essentially a constant voltage. The pulse width modulation approach defines a duty ratio of the interconnecting 20 switches as a linear function of the ratio of the time varying AC output and the stiff voltage. In the case of inverters, rectifiers, and frequency converters, the DC link capacitor is sized to store enough energy to maintain several tens of cycles of the AC quantity at the rated power, which requires 25 the use of large capacitors, commonly referred to as 'bulk' capacitors, and which tend to dominate the weight and volume of most converter technologies.

#### **SUMMARY**

In an example embodiment, a computer-readable medium is provided having stored thereon computer-readable instructions that when executed by a computing device, cause the computing device to control a converter. A first switch vector is selected based on a current, a voltage, or a power of a multi-phase load or a multi-phase power source. The first switch vector identifies a first state for each of a plurality of half-bridges of a converter as on or as off during 40 a first interval. A second switch vector is selected based on the current, the voltage, or the power of the multi-phase load or the multi-phase power source. The second switch vector identifies a second state for each of the plurality of halfbridges as on or as off during a second interval. The first 45 interval is computed based on the selected first switch vector. The second interval is computed based on the selected second switch vector. Each of the plurality of half-bridges is controlled as on or as off during the first interval based on the selected first switch vector. Each of the 50 plurality of half-bridges is controlled as on or as off during the second interval based on the selected second switch vector. The first interval and the second interval are selected for each switching period of the converter. The switching period is less than one millisecond. The first interval and the second interval are computed to either charge a link capacitor connected in parallel across the plurality of half-bridges to a predefined voltage from approximately zero or to discharge the link capacitor to approximately zero from the predefined voltage.

In another example embodiment, a conversion controller is provided. The conversion controller includes, but is not limited to, a processor and the computer-readable medium having stored thereon computer-readable instructions that 65 when executed by a computing device, cause the computing device to control a converter.

2

In yet another example embodiment, a converter device is provided. The converter device includes, but is not limited to, a converter, a link capacitor, and the conversion controller

Other principal features of the disclosed subject matter will become apparent to those skilled in the art upon review of the following drawings, the detailed description, and the appended claims.

#### BRIEF DESCRIPTION OF THE DRAWINGS

Illustrative embodiments of the disclosed subject matter will hereafter be described referring to the accompanying drawings, wherein like numerals denote like elements.

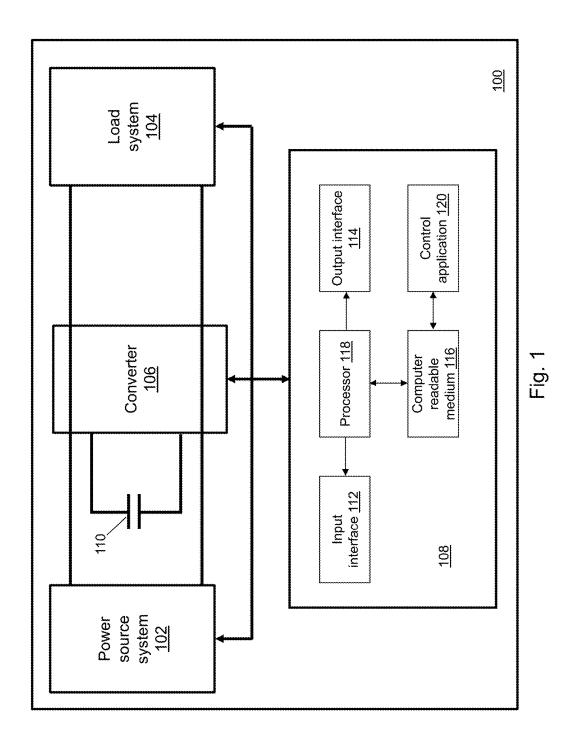

FIG. 1 is a block diagram of a power conversion system in accordance with an illustrative embodiment.

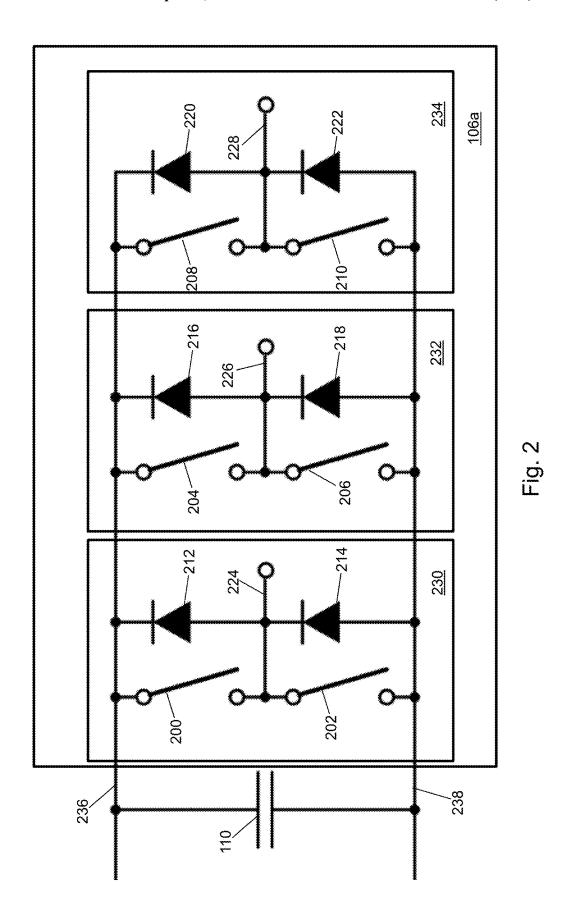

FIG. 2 is a circuit diagram of a part of a converter of the power conversion system of FIG. 1 in accordance with an illustrative embodiment.

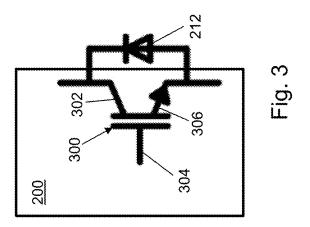

FIG. 3 is a first switch-diode circuit of the converter of FIG. 2 in accordance with an illustrative embodiment.

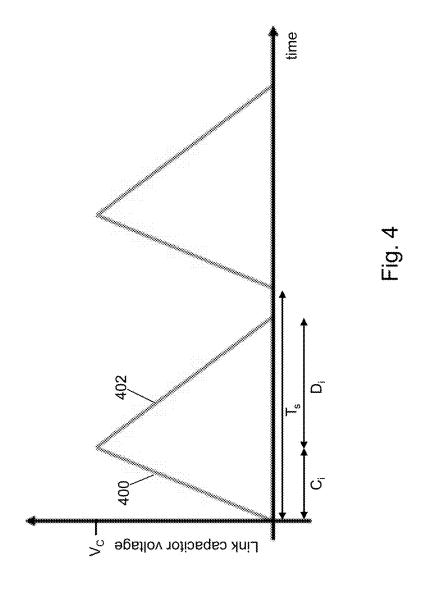

FIG. 4 shows a charging/discharging curve of a link capacitor of the power conversion system of FIG. 1 in accordance with an illustrative embodiment.

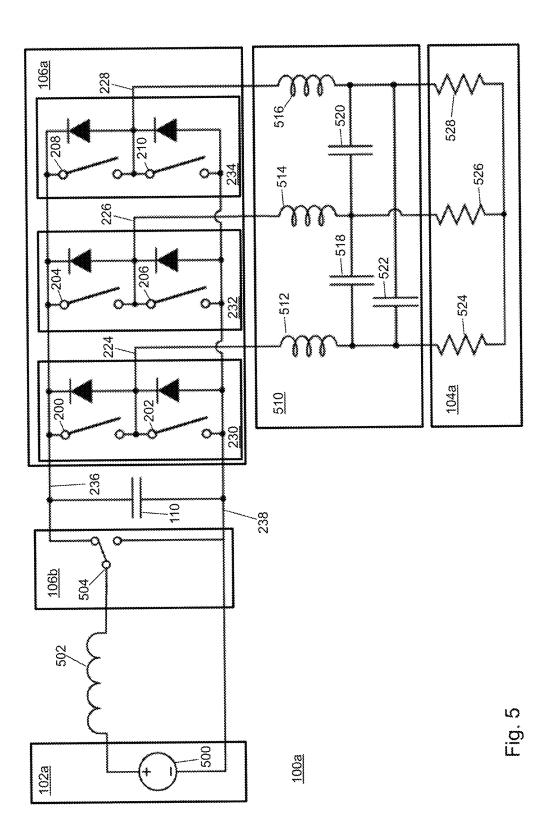

FIG. 5 is a block diagram of a first power conversion system in accordance with an illustrative embodiment.

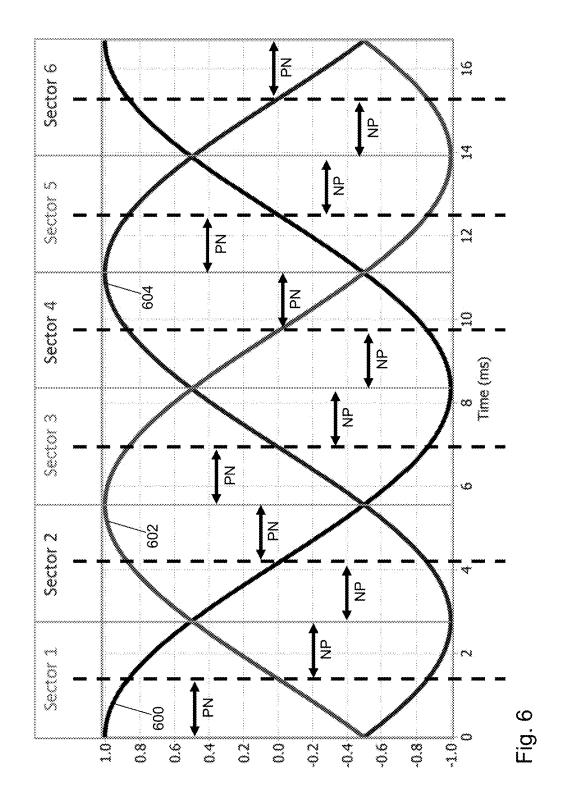

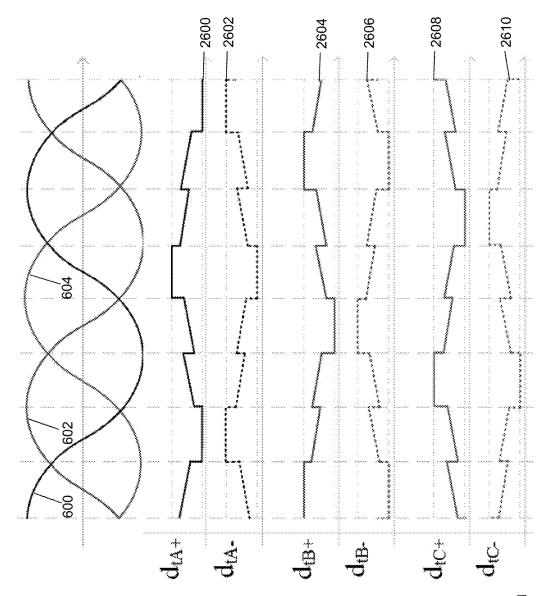

FIG. 6 shows a three-phase balanced set of sinusoidal voltage waveforms in accordance with an illustrative embodiment.

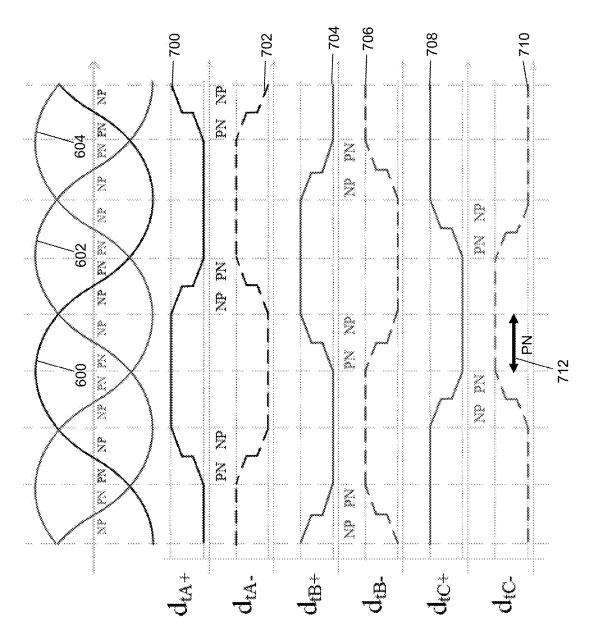

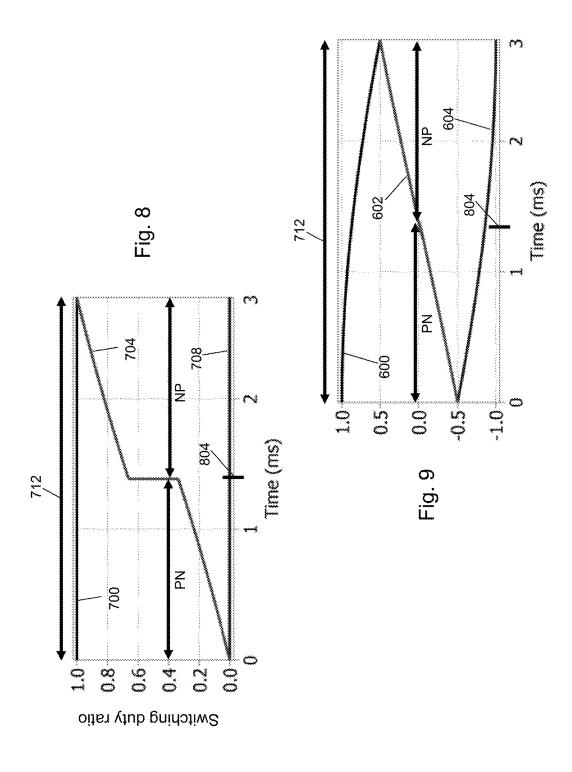

FIG. 7 shows a variation of duty ratio of the positive and negative throws of the converter of FIG. 2 in accordance with an illustrative embodiment.

FIG. **8** shows a zoomed portion of the duty ratio of FIG. **7** in accordance with an illustrative embodiment.

FIG. 9 shows a zoomed portion of the voltage waveforms of FIG. 6 in accordance with an illustrative embodiment.

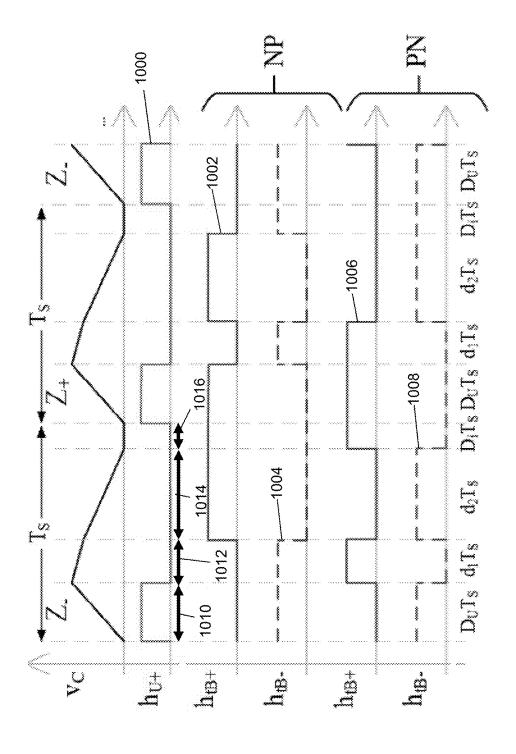

FIG. 10 shows two switching cycles for synthesizing an output waveform of the converter of FIG. 2 in accordance with an illustrative embodiment.

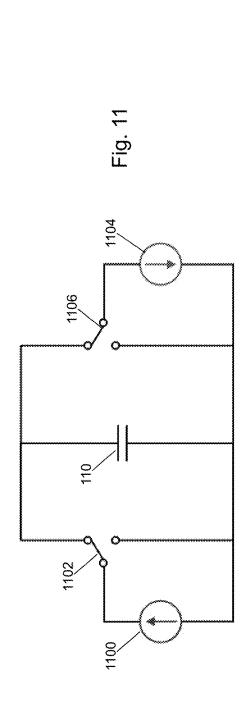

FIG. 11 is a circuit diagram of a simplified two subsystem power converter in accordance with an illustrative embodiment.

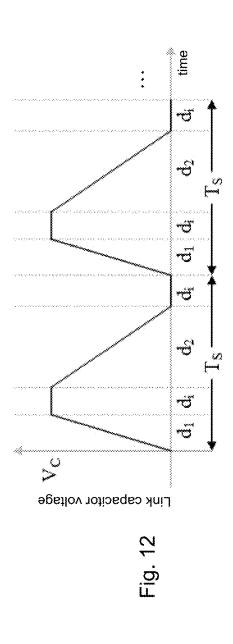

FIG. 12 shows a charging/discharging curve of a link capacitor of the power conversion system of FIG. 11 in accordance with an illustrative embodiment.

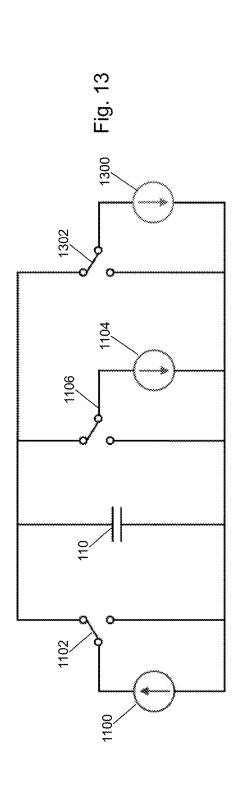

FIG. 13 is a circuit diagram of a simplified three subsystem power converter in accordance with an illustrative embodiment.

FIG. **14** shows a charging/discharging curve of a link capacitor of the power conversion system of FIG. **13** in accordance with an illustrative embodiment.

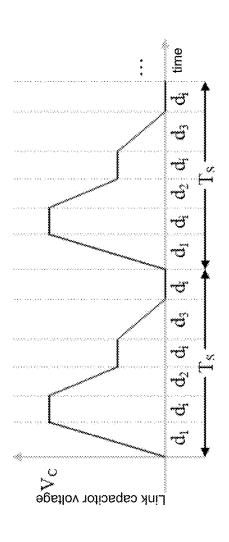

FIG. 15 shows a charging/discharging curve of a link capacitor of the power conversion system of FIG. 13 in accordance with a second illustrative embodiment.

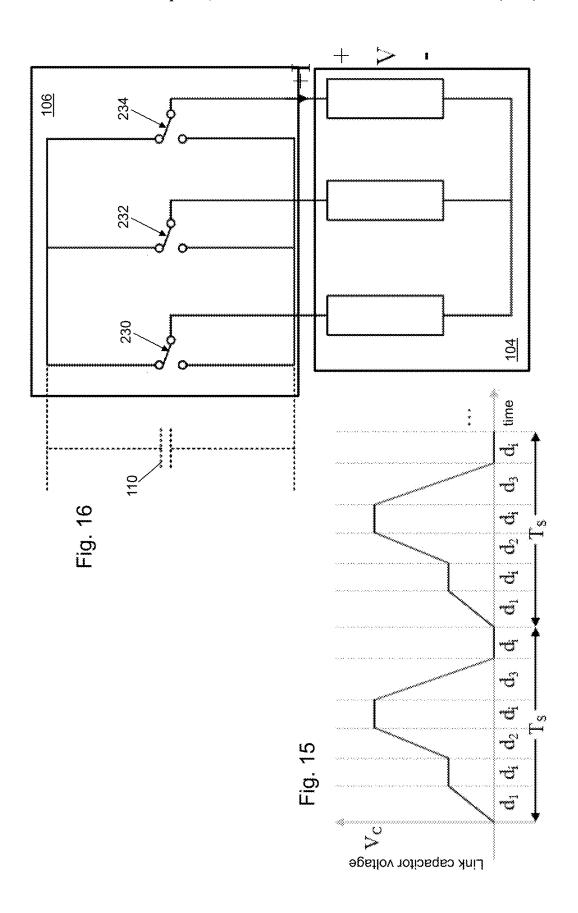

FIG. 16 is a block diagram of a simplified equivalent of a load system implemented for a three-phase AC system interfaced to the link capacitor through the converter in accordance with an illustrative embodiment.

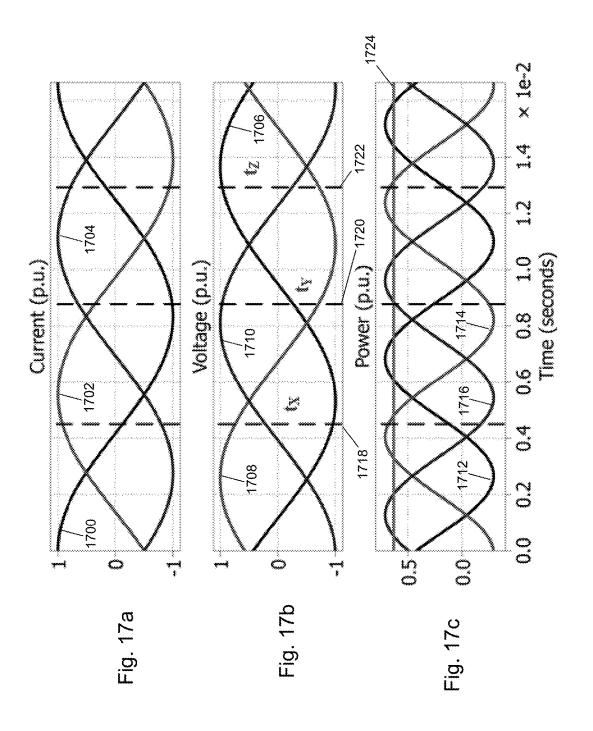

FIG. 17a shows a three-phase balanced set of sinusoidal 60 current waveforms in accordance with an illustrative embodiment.

FIG. 17b shows a three-phase balanced set of sinusoidal voltage waveforms in accordance with an illustrative embodiment.

FIG. 17c shows a three-phase balanced set of sinusoidal power waveforms in accordance with an illustrative embodiment.

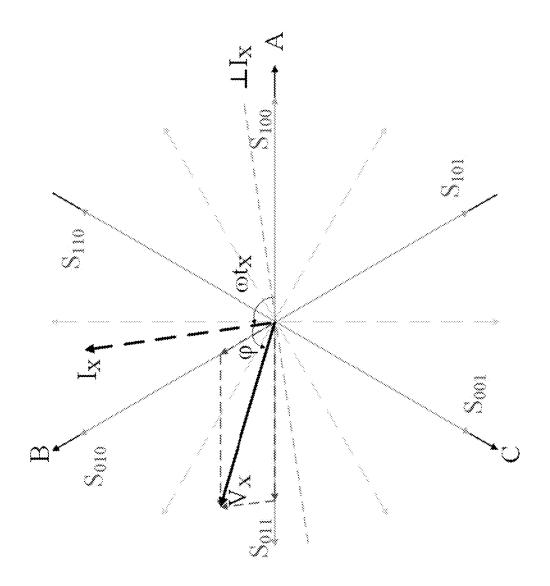

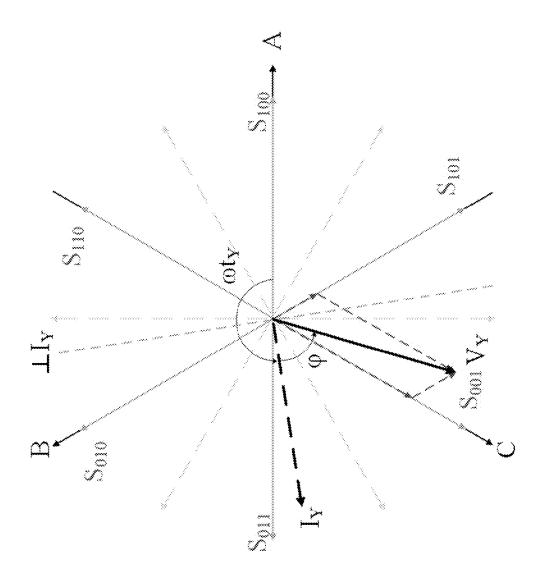

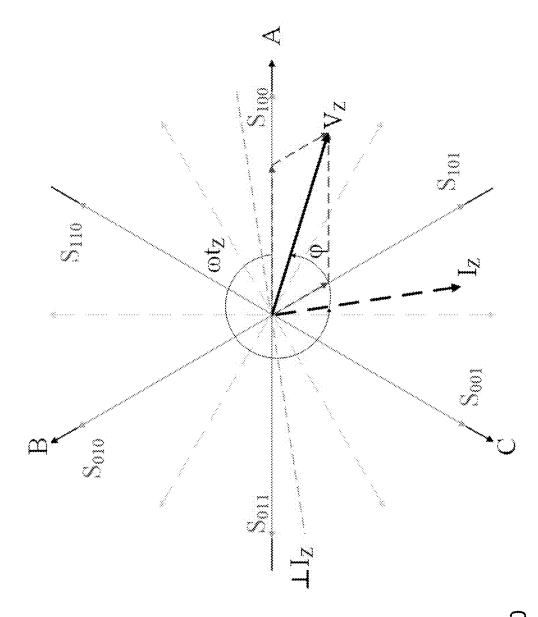

FIGS. 18-20 show vector parallelograms for three voltage and current vectors at different times in FIGS. 17a and 17b in an ABC space vector plane in accordance with an illustrative embodiment.

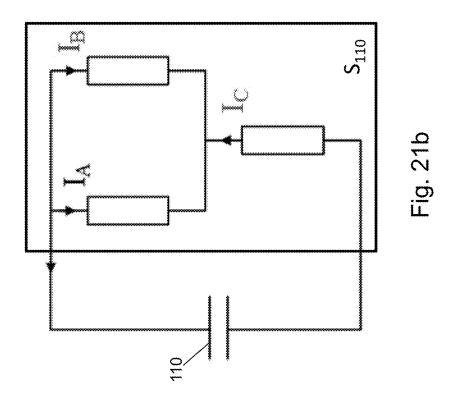

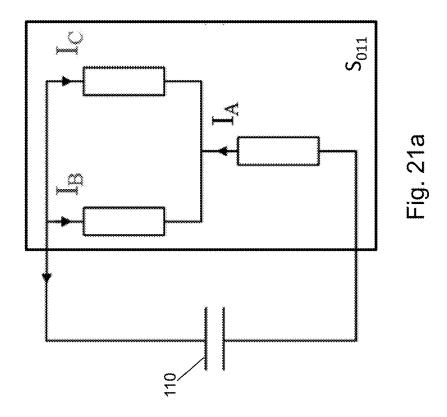

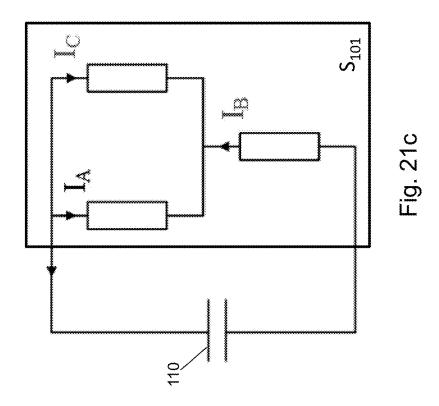

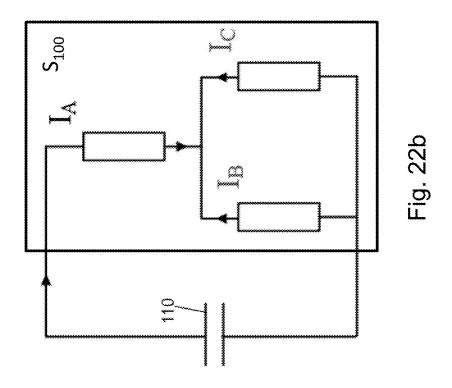

FIGS. **21***a***-21***c* show various converter configuration 5 models associated with switch vectors having two positive throws on in accordance with an illustrative embodiment.

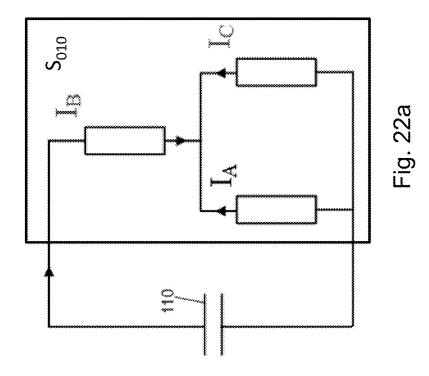

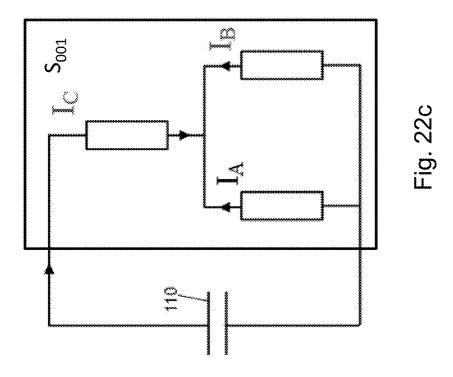

FIGS. **22***a***-22***c* show various converter configuration models associated with switch vectors having one positive throw on in accordance with an illustrative embodiment.

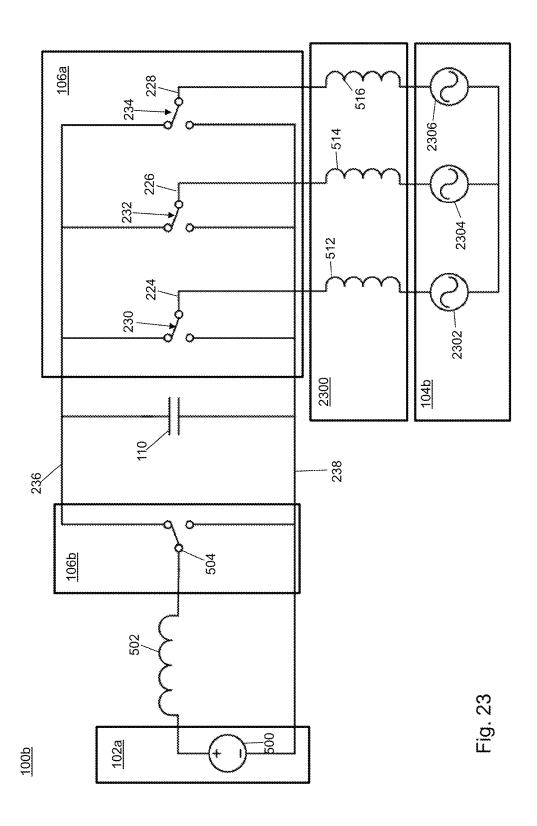

FIG. 23 is a block diagram of a second power conversion system in accordance with an illustrative embodiment.

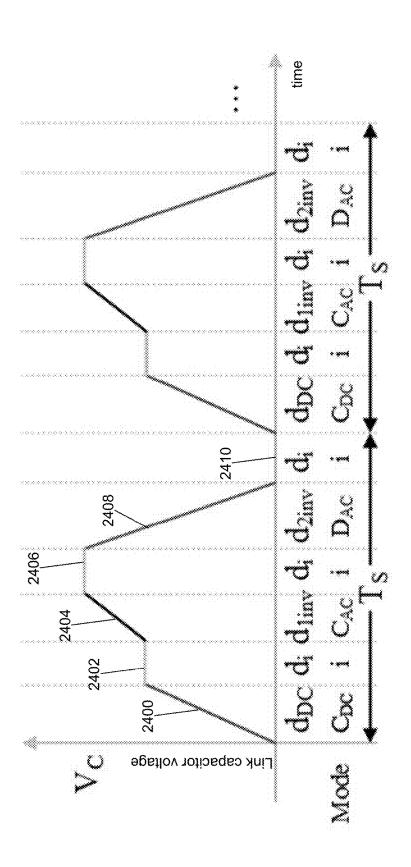

FIG. 24 shows a charging/discharging curve of a link capacitor of the power conversion system of FIG. 23 in accordance with a first illustrative embodiment.

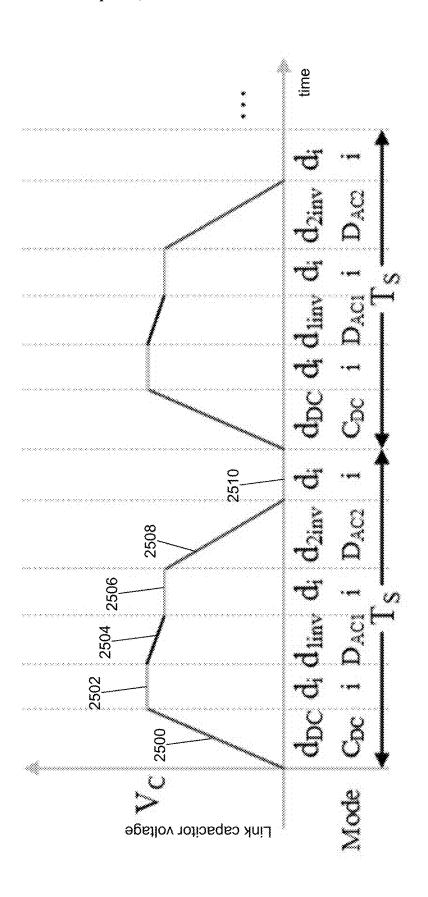

FIG. 25 shows a charging/discharging curve of a link capacitor of the power conversion system of FIG. 23 in accordance with a second illustrative embodiment.

FIG. **26***a* shows a variation of duty ratio of the positive and negative throws of the converter of the second power <sup>20</sup> conversion system of FIG. **23** in accordance with a first illustrative embodiment.

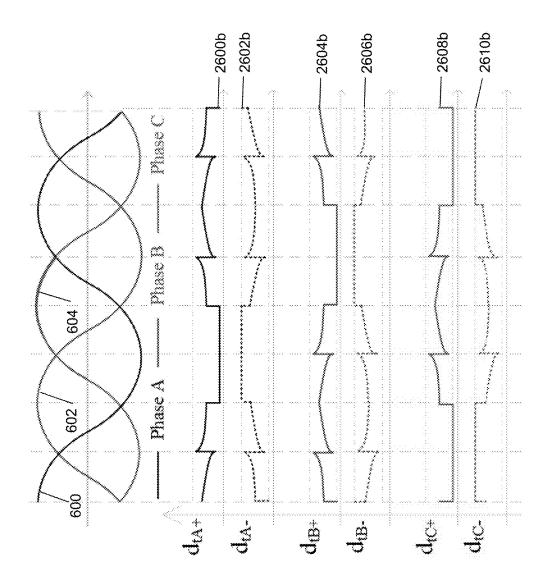

FIG. **26***b* shows a variation of duty ratio of the positive and negative throws of the converter of the second power conversion system of FIG. **23** in accordance with a second <sup>25</sup> illustrative embodiment.

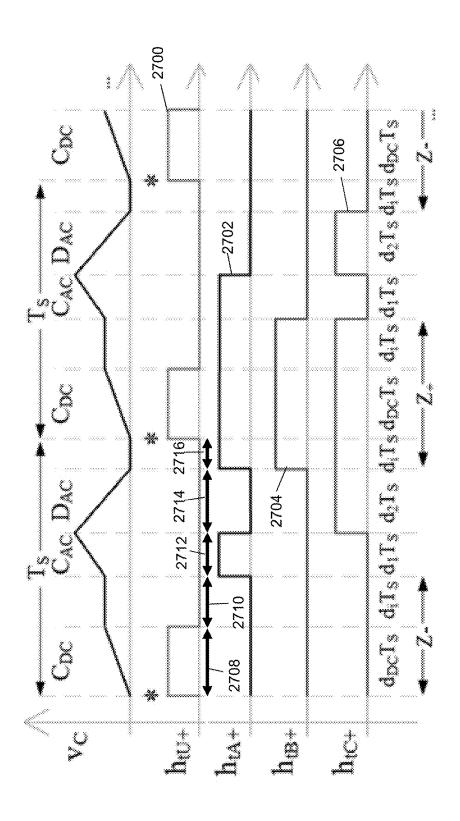

FIG. 27 shows switching functions to achieve the appropriate switch throws in accordance with a first illustrative embodiment.

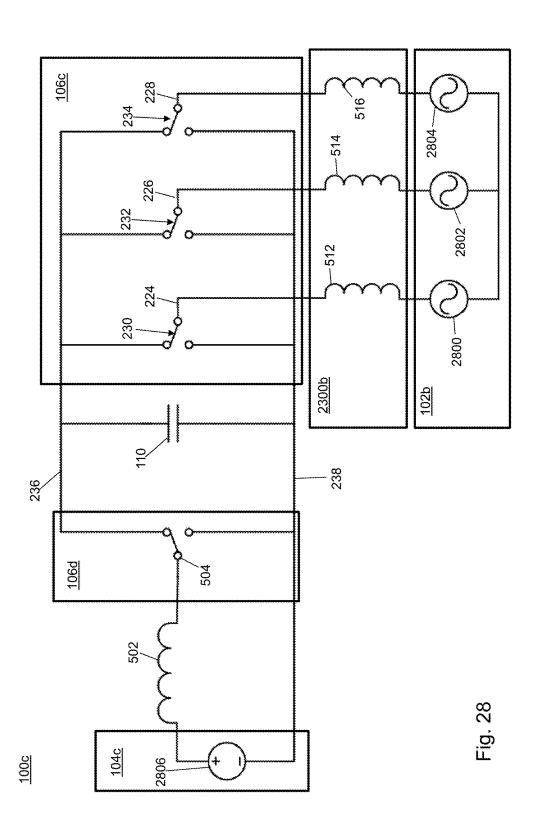

FIG. **28** is a block diagram of a third power conversion <sup>30</sup> system in accordance with an illustrative embodiment.

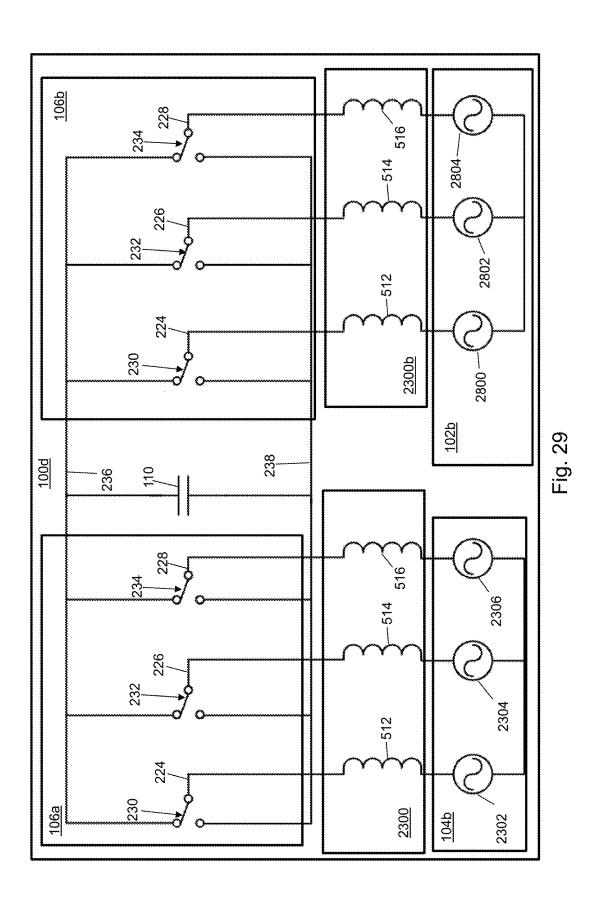

FIG. 29 is a block diagram of a fourth power conversion system in accordance with an illustrative embodiment.

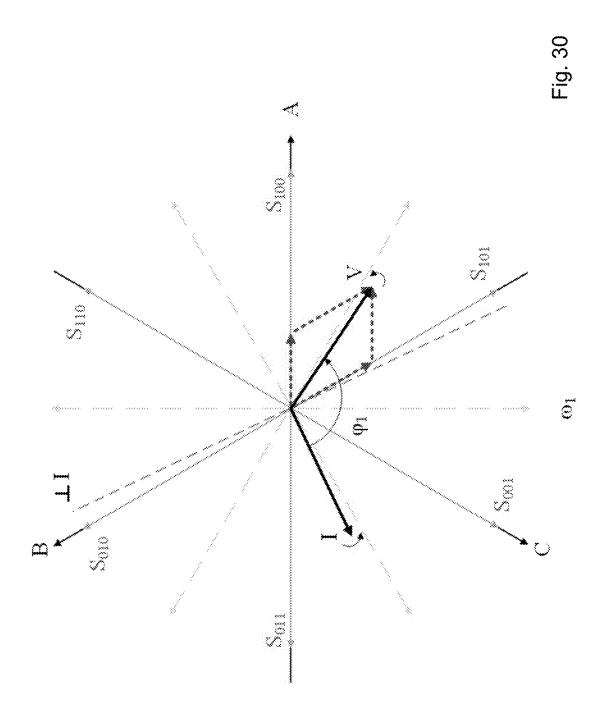

FIG. **30** shows a vector parallelogram for a voltage and current vector in an ABC space vector plane for the fourth <sup>35</sup> power conversion system of FIG. **29** in accordance with an illustrative embodiment.

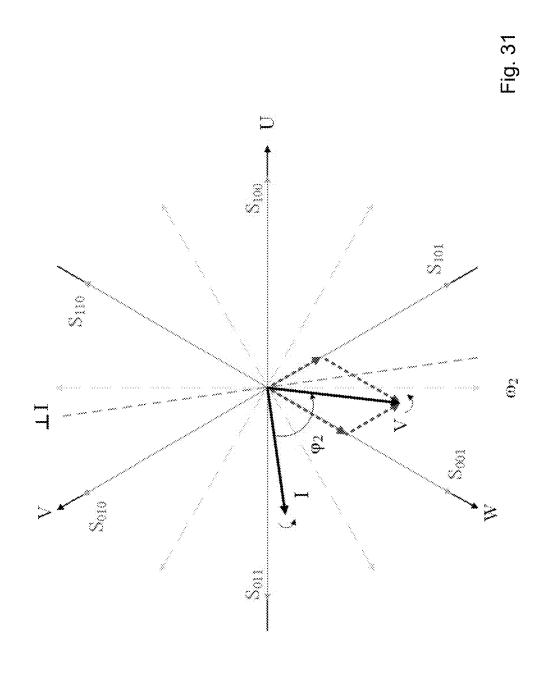

FIG. 31 shows a vector parallelogram for a voltage and current vector in an UVW space vector plane for the fourth power conversion system of FIG. 29 in accordance with an 40 illustrative embodiment.

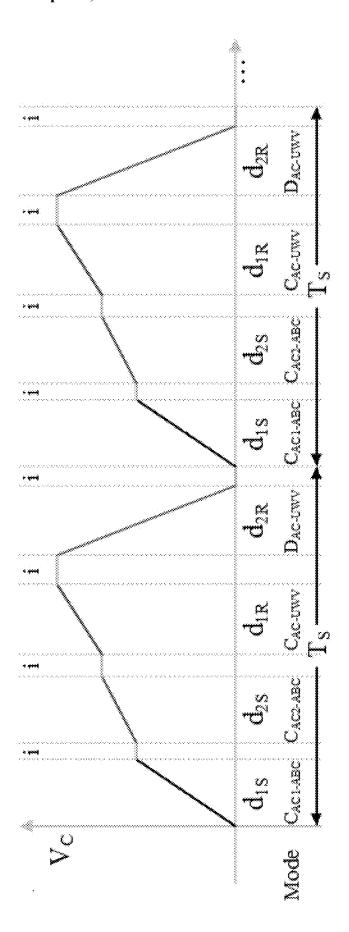

FIG. 32 shows a charging/discharging curve of a link capacitor of the fourth power conversion system of FIG. 29 in accordance with a second illustrative embodiment.

FIGS. **33-36** depict flow diagrams illustrating examples of 45 operations performed by a control application of the converter of the power conversion system of FIG. **1** in accordance with an illustrative embodiment

## DETAILED DESCRIPTION

Referring to FIG. 1, a power conversion system 100 may include a power source system 102, a load system 104, a converter 106, a conversion controller 108, and a link capacitor 110. Power source system 102 and load system 55 104 exchange energy through link capacitor 110 under control of conversion controller 108 and converter 106. Link capacitor 110 is connected in parallel with converter 106. A capacitance of link capacitor 110 may be many orders of magnitude less than traditional designs for power conversion 60 system 100.

Power source system 102 may include one or more alternating current (AC) and/or direct current (DC) source subsystems that provide electrical power. Load system 104 may include one or more AC and/or DC load subsystems that act as electrical loads. Some or all of power source system 102 and/or load system 104 may provide bidirec-

4

tional power flow such that a power source subsystem and/or a load subsystem may act as a source during a first time period and as a load during a second time period.

During normal operating conditions, a total power supplied by all of the subsystems acting as sources balance a total power consumed by all of the subsystems acting as loads. In the event that there is a mismatch between total source and load power levels, a storage subsystem may be added to power conversion system 100 to ensure overall power balance across link capacitor 110.

Conversion controller 108 may be electrically connected to power source system 102 and load system 104 to receive voltage, current, and/or power values used to define the parameters that control the energy transfer between power source system 102 and load system 104 based on the current availability/demand across power conversion system 100. The voltage, current, and/or power values may be received for each switching frequency interval or may be received less frequently depending on the dynamic needs of power conversion system 100. As a result, conversion controller 108 may dynamically control converter 106 to act as an inverter, a rectifier, and/or a frequency converter.

Conversion controller 108 is electrically connected to converter 106. Conversion controller 108 controls the supply of power by converter 106 from power source system 102 to load system 104 through command signals input to converter 106. The command signals are generated by conversion controller 108 based on the received voltage and current values or known voltage, current, and/or power values for power source system 102 and load system 104.

Conversion controller 108 may include an input interface 112, an output interface 114, a computer-readable medium 116, a processor 118, and a control application 120. Fewer, different, and additional components may be incorporated into conversion controller 108.

Input interface 112 provides an interface for receiving information from a user or from other devices for entry into conversion controller 108 as understood by those skilled in the art. Input interface 112 may interface with various input technologies including, but not limited to, a keyboard, a mouse, a display, a track ball, a keypad, one or more buttons, etc. to allow the user to enter information into conversion controller 108 or to make selections in a user interface displayed on the display. The same interface may support both input interface 112 and output interface 114. Conversion controller 108 may have one or more input interfaces that use the same or a different input interface technology. Additional inputs to conversion controller 108 may be the voltage, current, and/or power values received from power source system 102 and/or load system 104.

Output interface 114 provides an interface for outputting information for review by a user of conversion controller 108 and for input to another device. For example, output interface 114 may interface with various output technologies including, but not limited to, the display and a printer, etc. Conversion controller 108 may have one or more output interfaces that use the same or a different interface technology. Additional outputs from conversion controller 108 may be the command signals to converter 106.

Computer-readable medium 116 is an electronic holding place or storage for information so the information can be accessed by processor 118 as understood by those skilled in the art. Computer-readable medium 116 can include, but is not limited to, any type of random access memory (RAM), any type of read only memory (ROM), any type of flash memory, etc. such as magnetic storage devices (e.g., hard disk, floppy disk, magnetic strips, . . . ), optical disks (e.g.,

compact disc (CD), digital versatile disc (DVD), . . . ), smart cards, flash memory devices, cache memory, etc. Conversion controller 108 may have one or more computer-readable media that use the same or a different memory media technology. Conversion controller 108 also may have one or more drives that support the loading of a memory media such as a CD or DVD.

Processor 118 executes instructions as understood by those skilled in the art. The instructions may be carried out by a special purpose computer, logic circuits, or hardware 10 circuits. Processor 118 may be implemented in hardware and/or firmware, or any combination of these methods. The term "execution" is the process of running an application or the carrying out of the operation called for by an instruction. The instructions may be written using one or more program- 15 ming language, scripting language, assembly language, etc. Processor 118 executes an instruction, meaning it performs/ controls the operations called for by that instruction. Processor 118 operably couples with input interface 112, with output interface 114, and with computer-readable medium 20 116 to receive, to send, and to process information. Processor 118 may retrieve a set of instructions from a permanent memory device and copy the instructions in an executable form to a temporary memory device that is generally some form of RAM. Conversion controller 108 may include a 25 plurality of processors that use the same or a different processing technology.

Control application 120 performs operations associated with implementing some or all of the control of converter 106 as described with reference to FIGS. 33-35. The operations may be implemented using hardware, firmware, software, or any combination of these methods. Referring to the example embodiment of FIG. 1, control application 120 is implemented in software (comprised of computer-readable and/or computer-executable instructions) stored in computer-readable medium 116 and accessible by processor 118 for execution of the instructions that embody the operations of control application 120. Control application 120 may be written using one or more programming languages, assembly languages, scripting languages, etc.

Referring to FIG. 2, a circuit diagram of a part of converter 106 implemented as a first converter 106a is shown in accordance with an illustrative embodiment. First converter 106a is a three-phase converter. In the illustrative embodiment of FIG. 2, first converter 106a may include a 45 first half-bridge 230, a second half-bridge 232, and a third half-bridge 234. In the illustrative embodiment, converter 106 is first converter 106a though a different number of phases may be output from converter 106 in alternative embodiments including a DC current. For example, converter 106 may output two- or four-phase or DC waveforms. Converter 106 may include a half-bridge for each phase.

First half-bridge 230 includes a first switch-diode circuit and a second switch-diode circuit. The first switch-diode circuit includes a first top switch 200 and a first top diode 55 212 connected anti-parallel across first top switch 200. Referring to FIG. 3, the first switch-diode circuit is shown in accordance with an illustrative embodiment. First top switch 200 may be implemented as a transistor switch 300. Transistor switch 300 may include a drain 302, a gate 304, and a source 306 like a metal-oxide-semiconductor field-effect transistor (MOSFET) or include a collector 302, a gate 304, and an emitter 306 like an insulated-gate bipolar transistor (IGBT), or include a collector 302, a base 304, and an emitter 306 like a bipolar junction transistor. Depending on 65 the switching logic and whether transistor switch 300 is an n-type or a p-type, drain 302 and source 306 may be

6

reversed. A voltage applied to gate 304 determines a switching state of transistor switch 300. First top diode 212 is connected anti-parallel across source 306 and drain 302 of transistor switch 300. In an illustrative embodiment, transistor switch 300 is an insulated-gate field-effect transistor such as a MOSFET, IGBT, Gallium Nitride (GaN) device, Silicon Carbide (SiC) device, or other type of power semi-conductor switch.

Referring again to FIG. 2, in the illustrative embodiment, the second switch-diode circuit includes a first bottom switch 202 and a first bottom diode 214 connected antiparallel across first bottom switch 202 similar to the first switch-diode circuit. For illustration, first bottom switch 202 is also implemented as transistor switch 300. Source 306 of transistor switch 300 of the first switch-diode circuit is connected to drain 302 of transistor switch 300 of the second switch-diode circuit. Drain 302 of transistor switch 300 of the first switch-diode circuit is connected to a top line 236. Source 306 of transistor switch 300 of the second switchdiode circuit is connected to a bottom line 238. Gate 304 of transistor switch 300 of the first switch-diode circuit and gate 304 of transistor switch 300 of the second switch-diode circuit are connected to conversion controller 108 to receive gating signals to control a state of first top switch 200 and first bottom switch 202, respectively. At any point in time, only one of first top switch 200 and first bottom switch 202 is effectively closed. A first-phase line 224 is connected between source 306 of transistor switch 300 of the first switch-diode circuit and drain 302 of transistor switch 300 of the second switch-diode circuit. A direction of current flow from first-phase line 224 to top line 236 through first top switch 200 indicates first half-bridge 230 is charging link capacitor 110, and a direction of current flow from top line 236 to first-phase line 224 through first top switch 200 indicates first half-bridge 230 is discharging link capacitor 110. When first top switch 200 is effectively closed, first half-bridge 230 is 'On' or in a one '1' state. When first bottom switch 202 is effectively closed, first half-bridge 230 is 'Off' or in a zero '0' state.

Link capacitor 110 is connected in parallel with first converter 106a between top line 236 and bottom line 238. A half-bridge is included for each phase current output from converter 106. Second half-bridge 232 is identical to first half-bridge 230 and includes a third switch-diode circuit and a fourth switch-diode circuit. The third switch-diode circuit includes a second top switch 204 and a second top diode 216 connected anti-parallel across second top switch 204. The fourth switch-diode circuit includes a second bottom switch 206 and a second bottom diode 218 connected anti-parallel across second bottom switch 206. Again, second top switch 204 and second bottom switch 206 may be implemented as transistor switch 300 and connected in an identical manner to that described for first top switch 200 and first bottom switch 202.

Gate 304 of transistor switch 300 of the third switch-diode circuit and gate 304 of transistor switch 300 of the fourth switch-diode circuit are connected to conversion controller 108 to receive gating signals to control a state of second top switch 204 and second bottom switch 206, respectively. At any point in time, only one of second top switch 204 and second bottom switch 206 is effectively closed. A second-phase line 226 is connected between source 306 of transistor switch 300 of the third switch-diode circuit and drain 302 of transistor switch 300 of the fourth switch-diode circuit. A direction of current flow from second-phase line 226 to top line 236 through second top switch 204 indicates second half-bridge 232 is charging link capacitor 110, and a direc-

tion of current flow from top line 236 to second-phase line 226 through second top switch 204 indicates second half-bridge 232 is discharging link capacitor 110. When second top switch 204 is effectively closed, second half-bridge 232 is 'On' or in a one '1' state. When second bottom switch 206 is effectively closed, second half-bridge 232 is 'Off' or in a zero '0' state.

Third half-bridge 234 is identical to first half-bridge 230 and includes a fifth switch-diode circuit and a sixth switch-diode circuit. The fifth switch-diode circuit includes a third top switch 208 and a third top diode 220 connected antiparallel across third top switch 20. The sixth switch-diode circuit includes a third bottom switch 210 and a third bottom diode 222 connected anti-parallel across third bottom switch 210. Again, third top switch 208 and third bottom switch 210 may be implemented as transistor switch 300 and connected in an identical manner to that described for first top switch 200 and first bottom switch 202.

Gate 304 of transistor switch 300 of the fifth switch-diode circuit and gate 304 of transistor switch 300 of the sixth switch-diode circuit are connected to conversion controller 108 to receive gating signals to control a state of third top switch 208 and third bottom switch 210, respectively. At any point in time, only one of third top switch 208 and third bottom switch 210 is effectively closed. A third-phase line 228 is connected between source 306 of transistor switch 300 of the fifth switch-diode circuit and drain 302 of transistor switch 300 of the sixth switch-diode circuit. A direction of current flow from third-phase line 228 to top line 236 through third top switch 208 indicates third half-bridge 234 is charging link capacitor 110, and a direction of current flow from top line 236 to third-phase line 228 through third top switch 208 indicates third half-bridge 234 is discharging link capacitor 110. When third top switch 208 is effectively closed, third half-bridge 234 is 'On' or in a one '1' state. When third bottom switch 210 is effectively closed, third half-bridge 234 is 'Off' or in a zero '0' state.

Referring to FIG. 4, in normal operation, link capacitor 110 is charged to a voltage  $V_c$  as shown by charging curve 400. Voltage  $V_c$  stored by link capacitor 110 is then discharged as shown by discharging curve 402. Converter 106 controls the charge and discharge cycles for each switching period  $T_s$  that is the inverse of the switching frequency

$$f_s = \frac{1}{T_s}$$

.

In an illustrative embodiment,  $f_s$  is much higher than a 50 frequency of a power supplied  $f_p$  by power conversion system 100. For illustration,  $f_s$  is at least 1 kilohertz (kHz) resulting in a switching period of less than one millisecond while  $f_p$  may be 60 Hz.  $f_s$  can be at least 100 times  $f_p$  and can be variable.

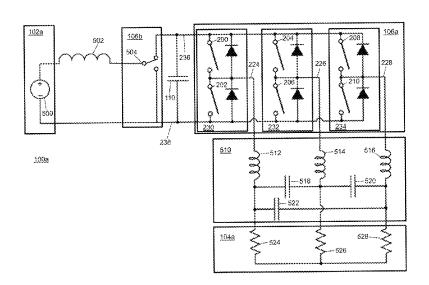

Referring to FIG. 5, a circuit diagram of a first power conversion system 100a is shown in accordance with a first illustrative embodiment. First power conversion system 100a may include a first power source system 102a, a first load system 104a, first converter 106a, a second converter 106b, conversion controller 108 (not shown in FIG. 5), and link capacitor 110. In the illustrative embodiment of FIG. 5, first power source system 102a includes a single source subsystem that includes a DC power source 500. Converter 106 is implemented as first converter 106a and second converter 106b, where second converter 106b is a one-phase converter. Inductor 502 and source control switch 504 are

connected in series with DC power source 500, which together can be visualized as a DC-DC boost chopper. Link capacitor 110 is connected in parallel with first converter 106a and second converter 106b, between top line 236 and bottom line 238. Source control switch 504 is connected to charge link capacitor 110 to voltage  $V_c$  in a first position as illustrated in FIG. 5 and to disconnect first power source system 102a from link capacitor 110 when in a second position. Source control switch 504 may be implemented as a single half-bridge.

In the illustrative embodiment of FIG. 5, first load system 104a includes a resistive load resulting in a unity power factor and a current and a voltage that are in-phase with each other. First load system 104a includes a first resistor 524, a second resistor 526, and a third resistor 528. An L-C filter 510 is connected between first converter 106a and first load system 104a to reduce a ripple current. L-C filter 510 includes a first inductor 512, a second inductor 514, a third inductor 516, a first capacitor 518, a second capacitor 520, a third capacitor 522. First inductor 512 is connected on first-phase line 224. Second inductor 514 is connected on second-phase line 226. Third inductor 516 is connected on third-phase line 228. First capacitor 518 is connected in parallel between first-phase line 224 and second-phase line 226 between first inductor 512 and first resistor 524 and second inductor 514 and second resistor 526. Second capacitor 520 is connected in parallel between second-phase line 226 and third-phase line 228 between second inductor 514 and second resistor 526 and third inductor 516 and third resistor 528. Third capacitor 522 is connected in parallel between first-phase line 224 and third-phase line 228 between first inductor 512 and first resistor 524 and third inductor 516 and third resistor 528. In some cases, capacitor 518, capacitor 520, and capacitor 522 may be optional. In cases where the load system is a three-phase motor, inductor 512, inductor 514 and inductor 516 may be the motor inductances.

Referring again to FIG. 4, a charge interval  $C_i$  is defined as  $d_C T_s$  where  $d_C$  is a charging duty ratio provided by connecting source control switch **504** to charge link capacitor **110**.

$$d_C = V_{in} \sqrt{\frac{2C}{P_{in}T_s}} \,,$$

where  $V_{in}$  is an input voltage provided by DC power source 500, C is a capacitance of link capacitor 110, and  $P_{in}=V_{in}I_{in}$  where  $I_{in}$  is an input current provided by DC power source 500. The charge interval  $C_i$  determines a net power that can be delivered to load system 104. A discharge interval  $D_i$  is defined as  $d_DT_s$  where  $d_D$  is a discharge duty ratio provided by controlling a duty ratio of first top switch 200, second top switch 204, and third top switch 208, which are the inverse of a duty ratio of first bottom switch 202, second bottom switch 206, and third bottom switch 204, and third top switch 208 may be referred to as positive throws, and first bottom switch 202, second bottom switch 206, and third bottom switch 206, and third bottom switch 207, second bottom switch 206, and third bottom switch 210 may be referred to as negative throws herein.

The operation of converter 106 within each switching period  $T_s$  follows a predetermined energy charge-discharge pattern through link capacitor 110. For example, during the charge interval  $C_i$ , the DC-DC boost chopper transfers energy to link capacitor 110 while first converter 106a is held in a zero state with each of the first switch-diode circuit,

the second switch-diode circuit, and the third switch-diode circuit held in the same state. Therefore, load system 104 does not receive any power through link capacitor 110 during the charge interval  $C_i$ . The link capacitor voltage across link capacitor 110 increases approximately linearly 5 from zero to  $V_c$  as shown by charging curve 400. Soon after the energy stored in link capacitor 110 reaches a sufficient and predetermined value, the DC-DC boost chopper is disconnected from link capacitor 110 by source control switch 504. The charge duty ratio can be independent of time 10 as long as input voltage, power throughput, and switching frequency are maintained constant.

During the discharge interval  $D_i$ , first power source system 102a does not exchange power with link capacitor 110 and the first switch-diode circuit, the second switch-diode 15 circuit, and the third switch-diode circuit are modulated by conversion controller 108 to provide a discharge path for the energy stored in link capacitor 110. The excess period when first converter 106a is not in either a discharge or a charge state, link capacitor 110 is in an idle state with the link 20 capacitor voltage maintained either at zero, at its peak  $V_c$ , or at an intermediate value.

To define the modulation of the first switch-diode circuit, the second switch-diode circuit, and the third switch-diode circuit by conversion controller 108, consider a three-phase 25 balanced set of sinusoidal voltage waveforms desired at the output as shown in FIG. 6. A first-phase output waveform (current, voltage, or power) 600 is created by operation of first half-bridge 230 and may be referred as an A-phase waveform. A second-phase output waveform 602 is created 30 by operation of second half-bridge 232 and may be referred as a B-phase waveform. A third-phase output waveform 604 is created by operation of third half-bridge 234 and may be referred as a C-phase waveform. As understood by a person of skill in the art, the current and voltage waveforms are 35 360/m degrees out of phase with each other, where m represents a number of phases. Thus,  $V_A$ ,  $V_B$ , and  $V_C$  and  $I_A$ ,  $I_B$ , and  $I_C$  are 120 degrees out of phase with each other.

A time interval of one period of the three-phase output waveforms can be divided into 6 sectors, depending on 40 which of the phase voltages is the most positive and which of the phase voltages is the most negative. Each of the 6 sectors may be further classified into 2 sub-sectors each, depending on either having two of the phase voltages positive or having two of the phase voltages negative, which 45 are labeled NP and PN, respectively.

Referring to FIG. 7, a variation of duty ratio of the positive and negative throws of first half-bridge 230, second half-bridge 232, and third half-bridge 234 are shown for an entire power frequency period. A first duty ratio curve 700 50 shows a variation in duty ratio of first top switch 200. A second duty ratio curve 702 shows a variation in duty ratio of first bottom switch 202, which is an inverse of first duty ratio curve 700. A third duty ratio curve 704 shows a variation in duty ratio of second top switch 204. A fourth 55 duty ratio curve 706 shows a variation in duty ratio of second bottom switch 206, which is an inverse of third duty ratio curve 704. A fifth duty ratio curve 708 shows a variation in duty ratio of third top switch 208. A sixth duty ratio curve 710 shows a variation in duty ratio of third 60 bottom switch 210, which is an inverse of fifth duty ratio curve 708.

The discharge interval duty ratio  $d_D$  and its distribution among the positive and negative throws of converter 106 is a function of the instantaneous output voltages of the 65 three-phases. A first switching period discharge cycle 712 illustrates a switching for Sector 1 shown referring to FIG.

10

6. Referring to FIG. 8, the duty ratio of first top switch 200, second top switch 204, and third top switch 208 are shown for first switching period discharge cycle 712 in accordance with an illustrative embodiment.

Referring to FIG. 9, for first switching period discharge cycle 712, first-phase output waveform 600 is the most positive, and third-phase output waveform 604 is the most negative. Second-phase output waveform 602 is negative for a first sub-sector (PN) and positive for a second sub-sector (NP). Referring again to FIG. 8, while distributing the energy stored by link capacitor 110 among the three-phases, first top switch 200 and third bottom switch 210 are closed (enabled) during the entire discharge interval for first switching period discharge cycle 712.

Second half-bridge 232 is toggled between second top switch 204 and second bottom switch 206 during the discharge interval for first switching period discharge cycle 712 in a predetermined manner that synthesizes the desired output waveform. For example, second top switch 204 is operated at the duty ratio indicated by third duty ratio curve 704, and second bottom switch 206 is operated at a duty ratio indicated by an inverse of third duty ratio curve 704. In alternative embodiments, third duty ratio curve 704 may have a different shape that transitions the duty ratio between second top switch 204 and second bottom switch 206 from approximately zero at a start time of Sector 1 to approximately one at an end time of Sector 1. For example, third duty ratio curve 704 may be curved and may or may not include a discontinuity as shown in the illustrative embodiment

Referring to FIG. 10, two switching cycles for synthesizing second-phase output waveform 602 in sector 1 are shown. A first switching function curve 1000 defines a switching function for source control switch 504. A second switching function curve 1002 defines a switching function for second top switch 204 during Sector 1 and the second sub-sector (NP). A third switching function curve 1004 defines a switching function for second bottom switch 206 during Sector 1 and the second sub-sector (NP), which is an inverse of the switching function for second top switch 204 during Sector 1 and the second sub-sector (NP). A fourth switching function curve 1006 defines a switching function for second top switch 204 during Sector 1 and the first sub-sector (PN). A fifth switching function curve 1008 defines a switching function for second bottom switch 206 during Sector 1 and the first sub-sector (PN), which is an inverse of the switching function for second top switch 204 during Sector 1 and the first sub-sector (PN).

A first time interval 1010 shows charge interval Ci. Discharge interval D<sub>i</sub> includes a second time interval 1012 and a third time interval 1014. Second time interval 1012 defines a time that second bottom switch 206 is closed when the output waveform is in Sector 1 and the second sub-sector (NP). Second time interval 1012 also defines a time that second top switch 204 is closed when the output waveform is in Sector 1 and the first sub-sector (PN). Third time interval 1014 defines a time that second top switch 204 is closed when the output waveform is in Sector 1 and the second sub-sector (NP). Third time interval 1014 also defines a time that second bottom switch 206 is closed when the output waveform is in Sector 1 and the first sub-sector (PN). A transition time **804** (shown referring to FIGS. **8** and 9) indicates a time that second half-bridge 232 toggles between the second sub-sector (NP) and the first sub-sector (PN).

The expression for a duty ratio for second time interval 1012 during Sector 1 and the first sub-sector (PN) may be defined as

$$d_1^{PN} = V_{out} \sqrt{\frac{9C}{T_s P_{in}} \left[ \frac{1 - \sqrt{\cos^2\theta - \frac{\sin\theta \cos\theta}{\sqrt{3}}}}{\frac{1}{2}\cos\theta + \frac{\sqrt{3}}{2}\sin\theta} \right]}$$

where  $V_{\it out}$  is an output voltage, and  $\theta$  is an electrical angle of the output voltage waveform.

The expression for a duty ratio for second time interval 1012 during Sector 1 and the second sub-sector (NP) may be defined as

$$d_1^{NP} = V_{out} \sqrt{\frac{9C}{T_r P_{in}} \left[ \frac{1 - \sqrt{\sin^2 \theta - \frac{\sin \theta \cos \theta}{\sqrt{3}}}}{\cos \theta} \right]}.$$

Third time interval 1014 is defined as the instant at which the voltage  $V_c$  across link capacitor 110 reaches zero. A fourth time interval 1016 defines an idle time between the discharge interval and the next charge interval and may be computed as  $T_s$  minus first time interval 1010 minus second time interval 1012 minus third time interval 1014. After link capacitor 110 is completely discharged, power source system 102 remains in its idle state, and converter 106 is in a zero state until the next switching period begins. Fourth time interval 1016 may be distributed as a dead time between the charge and discharge intervals, and/or between second time interval 1012 and third time interval 1014 as desired without affecting waveform synthesis.

The three-phase waveforms in successive sectors are either the same or mirror images of each other with only the phase arrangement different between sectors. Due to the 40 waveform symmetry, the modulation developed for Sector 1 for the first sub-sector (PN) and the second sub-sector (NP) can be extended to the remaining sectors by mapping the solution through appropriate translations and sign reversals for the appropriate phase.

First converter  ${\bf 106}a$  is maintained in the zero state during charge interval  $C_i$  and during any idle time. A zero state occurs when each throw of first half-bridge  ${\bf 230}$ , second half-bridge  ${\bf 232}$ , and third half-bridge  ${\bf 234}$  are in the same position, which occurs when first top switch  ${\bf 200}$ , second top 50 switch  ${\bf 204}$ , and third top switch  ${\bf 208}$  are all closed (enabled) or when first bottom switch  ${\bf 202}$ , second bottom switch  ${\bf 206}$ , and third bottom switch  ${\bf 210}$  are all closed (enabled). The zero state may alternate between a  $Z_+$  position (first top switch  ${\bf 200}$ , second top switch  ${\bf 204}$ , and third top switch  ${\bf 208}$  sall closed), and a  $Z_-$  position (first bottom switch  ${\bf 202}$ , second bottom switch  ${\bf 206}$ , and third bottom switch  ${\bf 201}$  all closed) every other switching period.

The principle of operation of converter 106 further may be described using a simple power converter that transfers 60 power between ideal current sources using ideal switches to interface between them and link capacitor 110. The topology of a simplified two subsystem power converter is illustrated in FIG. 11. This topology includes a first ideal current source 1100, a first switch 1102, link capacitor 110, a second ideal 65 current source 1104, and a second switch 1106. A power transfer takes place from first ideal current source 1100 to

12

second ideal current source 1104. As a result, first ideal current source 1100 provides energy and second ideal current source 1104 consumes energy. The ideal current sources may be realized using inductors in series with loads or voltage sources, for example, as described above referring to DC power source 500 and inductor 502 of FIG. 5.

First switch 1102 and second switch 1106 operate in a repetitive manner with a regulated duty ratio each switching period T<sub>s</sub>. First switch 1102 and second switch 1106 may be realized using power semiconductors such as MOSFETs and IGBTs as appropriate, for example, as described above. For example, first switch 1102 and second switch 1106 may correspond to first half-bridge 230 that includes first top switch 200 and first bottom switch 202. Other switch configurations can be selected based on a direction of current flow as understood by a person of skill in the art.

In every high frequency switching cycle, one current source supplies energy to link capacitor 110 during a first time interval  $d_1$  shown referring to FIG. 12. During first time interval  $d_1$ , first ideal current source 1100 is connected to a positive throw of first switch 1102 thereby connecting first ideal current source 1100 to charge link capacitor 110 to voltage  $V_c$ . During first time interval  $d_1$ , second ideal current source 1104 is connected to a negative throw of second switch 1106 and is thereby disconnected from link capacitor 110. Assuming a constant current output from first ideal current source 1100, the voltage across link capacitor 110 sees a linear rise in voltage. Neither first ideal current source 1100 nor second ideal current source 1104 is connected to charge or discharge link capacitor 110 during an idle time interval  $d_i$  shown referring to FIG. 12.

As a convention, the current flowing into link capacitor 110 is considered negative while the current flowing out of link capacitor 110 is considered positive. Similarly, the power delivered into link capacitor 110 is considered negative while the power delivered by link capacitor 110 is considered positive.

During first time interval  $d_1$ ,

$$I_1 = C \frac{dv_c}{dt} = C \frac{0 - V_{c1}}{d_1 T_*} \tag{1}$$

$$P_1 = \frac{C}{2T_s} [0 - V_{c1}^2] = -\frac{I_1^2 d_1^2 T_s}{2C}$$

(2)

where  $I_1$  is the current output from first ideal current source 1100, and  $P_1$  is an average net power transferred to link capacitor 110. It can be observed that both  $I_1$  and  $P_1$  are negative since current source  $I_1$  charges link capacitor 110.

During a second time interval d<sub>2</sub> shown referring to FIG. 12, second ideal current source 1104 is connected to a positive throw of second switch 1106 thereby connecting second ideal current source 1104 to discharge link capacitor 110 to zero. During a second time interval d<sub>2</sub> shown referring to FIG. 12, first ideal current source 1100 is connected to a negative throw of first switch 1102 thereby disconnecting first ideal current source 1100 from link capacitor 110. After second time interval d<sub>2</sub>, a second idle time interval d<sub>1</sub> may be entered before a next charge cycle of a next switching cycle.

During second time interval d<sub>2</sub>,

$$I_2 = C\frac{dv_c}{dt} = C\frac{V_{c1} - 0}{dsT_c}$$

(3)

-continued

$$P_2 = \frac{C}{2T_s} V_{\rm cl}^2 = \frac{I_s^2 d_2^2 T_s}{2C} \tag{4}$$

where  $I_2$  is the current output from second ideal current source **1104**, and  $P_2$  is an average net power transferred from link capacitor **110**. It can be observed that both  $I_2$  and  $P_2$  are positive since current source  $I_2$ , discharges link capacitor **110**. For balanced power,

$$I_1d_1+I_2d_2=0$$

.

The topology of a simplified three subsystem power converter is illustrated in FIG. 13. This topology includes first ideal current source 1100, first switch 1102, link capacitor 110, second ideal current source 1104, second switch 1106, a third ideal current source 1300, and a third switch 1302. A power transfer takes place from first ideal current source 1100 to second ideal current source 1104 and to third ideal current source 1300. As a result, first ideal current source 1100 provides energy and second ideal current source 1104 and third ideal current source 1300 consume energy.

First switch 1102, second switch 1106, and third switch 1302 operate in a repetitive manner with a regulated duty  $_{25}$  ratio each switching period  $T_s$ . Again, in every high frequency switching cycle, first ideal current source 1100 supplies energy to link capacitor 110 during a first time interval  $d_1$ , shown referring to FIG. 14.

During second time interval  $d_2$ , shown referring to FIG. 30 14, second ideal current source 1104 is connected to the positive throw of second switch 1106 thereby connecting second ideal current source 1104 to discharge link capacitor 110 to  $V_{c2}$ . During second time interval  $d_2$ ,

$$I_2 = C \frac{dv_c}{dt} = C \frac{V_{c1} - V_{c2}}{dzT_c}$$

(5)

$$P_2 = \frac{C}{2T_s} [V_{c1}^2 - V_{c2}^2] = -\frac{I_1 I_2 d_1 d_2 T_s}{2C} - \frac{I_2^2 d_2^2 T_s}{2C}$$

(6)

where  $\rm I_2$  is the current output from second ideal current source 1104,  $\rm V_{c2}$  is a remaining capacitor voltage at an end of  $\rm d_2$ , and  $\rm P_2$  is an average net power transferred from link 45 capacitor 110 to second ideal current source 1104. During third time interval  $\rm d_3$ , shown referring to FIG. 14, third ideal current source 1300 is connected to the positive throw of third switch 1302 thereby connecting third ideal current source 1300 to discharge link capacitor 110 from  $\rm V_{c2}$  to zero. 50 During third time interval  $\rm d_3$ ,

$$I_3 = C \frac{dv_c}{dt} = C \frac{V_{c2} - 0}{d_3 T_s} \tag{7}$$

$$P_3 = \frac{C}{2T_c} V_{c2}^2 = \frac{I_3^2 d_3^2 T_s}{2C} \tag{8}$$

where  $I_2$  is the current output from second ideal current 60 source  ${\bf 1104}$ , and  $P_3$  is an average net power transferred from link capacitor  ${\bf 110}$  to third ideal current source  ${\bf 1300}$ . It can be observed that since both the current sources  $I_2$  and  $I_3$  discharge the capacitor, currents  $I_2$  and  $I_3$  and powers  $P_2$  and  $P_3$  are positive. For balanced power,

14

Determining the duty ratio of the positive throws of first switch 1102, second switch 1106, and third switch 1302 for the desired power transfer can be derived using Equations 2, 6, and 8 as

$$d_1 = \sqrt{-\frac{2CP_1}{T_s I_1^2}} \tag{9}$$

$$d_2 = -\frac{I_1 d_1}{I_2} \left[ 1 - \sqrt{1 + \frac{P_2}{P_1}} \right] \tag{10}$$

$$d_3 = \sqrt{\frac{2CP_3}{T_s l_3^2}} \tag{11}$$

In the topology of FIG. 13, as another option, a power transfer could take place from first ideal current source 1100 and second ideal current source 1104 to third ideal current source 1300. As a result, first ideal current source 1100 and second ideal current source 1104 provide energy and third ideal current source 1300 consumes energy.

Again first switch 1102, second switch 1106, and third switch 1302 operate in a repetitive manner with a regulated duty ratio each switching period  $T_s$ . In every high frequency switching cycle, first ideal current source 1100 and second ideal current source 1104 supply energy to link capacitor 110 during first time interval  $d_1$  and second time interval  $d_2$ , shown referring to FIG. 15.

During first time interval d<sub>1</sub>,

$$I_1 = C \frac{dv_c}{dt} = C \frac{0 - V_{c1}}{dt T_c}$$

(12)

$$P_1 = -\frac{C}{2T_s}V_{c1}^2 = -\frac{I_1^2d_1^2T_s}{2C}$$

(13)

where  $I_1$  is the current output from first ideal current source 1100, and  $P_1$  is an average net power transferred to link capacitor 110 from first ideal current source 1100. It can be observed that both  $I_1$  and  $P_1$  are negative since current source  $I_1$  charges link capacitor 110.

During second time interval d<sub>2</sub> of FIG. 15,

$$I_2 = C \frac{dv_c}{dt} = C \frac{V_{c1} - V_{c2}}{d_2 T_s} \tag{14}$$

$$P_2 = \frac{C}{2T_s} [V_{c1}^2 - V_{c2}^2] = -\frac{I_1 I_2 d_1 d_2 T_s}{2C} - \frac{I_2^2 d_2^2 T_s}{2C}$$

(15)

here  $I_2$  is the current output from second ideal current source 1104,  $V_{c2}$  is a capacitor voltage at an end of  $d_2$ , and  $P_2$  is an average net power transferred to link capacitor 110 from second ideal current source 1104.

During third time interval  $d_3$ , shown referring to FIG. 15, second ideal current source 1104 is connected to the positive throw of second switch 1106 thereby connecting second ideal current source 1104 to discharge link capacitor 110 to zero. During third time interval  $d_3$ ,

$$I_3 = C \frac{dv_c}{dt} = C \frac{V_{c2} - 0}{d_3 T_s}$$

(16)

-continued

$$P_3 = \frac{C}{2T_s} V_{c2}^2 = \frac{I_3^2 d_3^2 T_s}{2C} \tag{17}$$

where  $I_3$  is the current output from third ideal current source 1104, and  $P_3$  is an average net power transferred from link capacitor 110 to third ideal current source 1300. It can be observed that since the current source  $I_2$  charges link capacitor 110,  $I_2$  and  $P_2$  are negative. Since the current source  $I_3$  10 discharges link capacitor 110,  $I_3$  and  $P_3$  are positive. For balanced power,

$$I_1d_1+I_2d_2+I_3d_3=0$$

.

Determining the duty ratio of the positive throws of first 15 switch 1102, second switch 1106, and third switch 1302 for the desired power transfer of FIG. 15 can be derived using Equations 13, 15, and 17 as

$$d_1 = \sqrt{-\frac{2CP_1}{T_s l_1^2}} \tag{18}$$

$$d_2 = -\frac{I_1 d_1}{I_2} \left[ 1 - \sqrt{1 + \frac{P_2}{P_1}} \right] \tag{19}$$

$$d_3 = \sqrt{\frac{2CP_3}{T_s l_3^2}} \tag{20}$$

While the illustrations of FIGS. 11 and 13 discuss a switching sequence for converter 106 for two to three subsystems, the approach can be extended to incorporate converters with any number of subsystems.

A simplified equivalent of load system 104 implemented 35 for a three-phase AC system interfaced to link capacitor 110 through converter 106 is shown in FIG. 16. At any instant of time, one of the throws of each of first half-bridge 230, second half-bridge 232, and third half-bridge 234 are closed (enabled, turned on). As discussed with reference to FIG. 5, 40 if all of the positive throws of first half-bridge 230, second half-bridge 232, and third half-bridge 234 are turned on simultaneously, or if all of the negative throws of first half-bridge 230, second half-bridge 232, and third halfbridge 234 are turned on simultaneously, load system 104 is isolated from link capacitor 110. Conversely, if all of the positive and negative throws are not in the same position simultaneously, there is net current flow to or from load system 104. In such cases, based on the magnitude and direction of the currents in each of the three phases of load 50 system 104, the entire three-phase subsystem of load system 104 presents itself as a single current source or load at that particular instant of time.

Furthermore, since the switching frequency of converter 106 is several orders of magnitude higher than the AC output 55 frequency, an AC current can be assumed to be constant during each high frequency switching cycle, which forms a foundation for extending the DC subsystem modulation approach presented above to a multi-phase source or load system.

Every multi-phase AC system operates at a particular power factor. For example, the resistive load of FIG. 5 operates at a unity power factor. The power factor determines whether the AC system is supplying power or consuming power at that instant of time, regardless of the direction of the overall power flow. In other words, a certain amount of power (a.k.a. reactive power) is delivered by the

16

multi-phase system to the external circuit which is taken back by the system without affecting the overall average or real power exchange.

For illustration, a first-phase current curve 1700, a second-phase current curve 1702, and a third-phase current curve 1704 are shown in FIG. 17a. A first-phase voltage curve 1706, a second-phase voltage curve 1708, and a third-phase voltage curve 1710 are shown in FIG. 17b. A first-phase power curve 1712, a second-phase power curve 1714, and a third-phase power curve 1716 are shown in FIG. 17c that result from first-phase current curve 1700, secondphase current curve 1702, and third-phase current curve 1704 in combination with first-phase voltage curve 1706, second-phase voltage curve 1708, and third-phase voltage curve 1710. The illustrative current and voltage waveforms operate at a particular power factor. FIG. 17c further includes an average real power curve 1724. Referring to FIGS. 17a and 17b, a power factor angle between the voltage and current vectors, denoted φ, is less than 90 20 degrees indicating that the three-phase AC system illustrated by FIGS. 17a-17c is consuming power so that converter 106 is in an inverter mode of operation.

To visualize the selection of switch positions for first half-bridge 230, second half-bridge 232, and third halfbridge 234 to ensure an appropriate transfer of power to the three-phase AC system, it is convenient to view the threephase voltage and current waveforms as being generated by space vectors rotating at a nominal angular frequency co of the three-phase AC system. Such representation is illustrated in FIG. 18 at a first time instant 1718, t, (shown referring to FIG. 17b) and shows the current vector  $I_x$  and voltage vector V<sub>x</sub>. Such representation is illustrated in FIG. 19 at a second time instant 1720,  $t_v$ , (shown referring to FIG. 17b) and shows the current vector  $I_{\nu}$  and voltage vector  $V_{\nu}$ . Such representation is illustrated in FIG. 20 at a third time instant 1722, t<sub>z</sub>, (shown referring to FIG. 17b) and shows the current vector Iz and voltage vector Vz. In the ABC space vector plane of FIGS. 18-20, the individual phase currents and voltages are simply the projections of the respective current and voltage space vector on the A, B, and C axes respectively. The current and voltage vectors together move counter-clockwise with the progression of time. As the space vector rotates, it traverses six different sectors (I-VI) that are delineated by the A, B and C axis. Six switch vectors are indicated as  $S_{100}$ ,  $S_{110}$ ,  $S_{010}$ ,  $S_{011}$ ,  $S_{001}$ , and  $S_{101}$ .

The selection of a particular set of positive or negative throws of first half-bridge 230, second half-bridge 232, and third half-bridge 234 leads to application of a particular voltage to the three-phase AC system that is located along six particular directions that lie along the axes of the three phases in positive and negative directions. The labels of the 'switch vectors'  $S_{ABC}$  represent the positions of the throws of first half-bridge 230, second half-bridge 232, and third half-bridge 234 that correspond to a particular direction of voltage being applied to the three-phase AC system. For example,  $S_{101}$  indicates that first top switch 200 (positive throw) of first half-bridge 230 is closed (enabled, on), second bottom switch 206 (negative throw) of second halfbridge 232 is closed (enabled, on), and third top switch 208 60 (positive throw) of third half-bridge 234 is closed (enabled, on). As another example,  $S_{011}$  indicates that first bottom switch 202 (negative throw) of first half-bridge 230 is closed (enabled, on), second top switch 204 (positive throw) of second half-bridge 232 is closed (enabled, on), and third top switch 208 (positive throw) of third half-bridge 234 is closed (enabled, on). As still another example, S<sub>110</sub> indicates that first top switch 200 (positive throw) of first half-bridge 230

is closed (enabled, on), second top switch 204 (positive throw) of second half-bridge 232 is closed (enabled, on), and third bottom switch 210 (negative throw) of third half-bridge 234 is closed (enabled, on).

An axis perpendicular to the current vector bisects the 5 ABC space vector plane into two half-planes. Selection of any of the three switch vectors that lie on the half-plane in which the current vector is located lead to discharging the link capacitor, while selection of the three switch vectors on the other half plane lead to charging the link capacitor. On 10 this basis, switch vectors may be termed discharging and charging switch vectors.

To ensure the right amount of power flow in the threephases during each switching period, the state of the switches for the three-phases is determined and the corresponding switch vectors selected accordingly. There are multiple choices of switch vectors that may be selected to obtain the desired voltage vector. The choice of switch vector combinations may be made depending on the desired application requirements which may be limited by a peak 20 voltage across link capacitor 110, to minimize losses in converter 106, by a duty ratio behavior, etc. The simplest choice of the switch vectors which will provides the desired voltage vector, and thus, the desired power throughput can be the two switch vectors that are nearest to the desired 25 voltage vector in the space vector plane. For example, at first time instant 1718,  $t_x$ , switch vectors  $S_{011}$  and  $S_{010}$  may be selected; at second time instant 1720,  $t_y$ , switch vectors  $S_{101}$ and  $S_{001}$  may be selected; and, at third time instant 1722,  $t_z$ , switch vectors  $S_{101}$  and  $S_{100}$  may be selected. The desired 30 voltage vector may also be obtained from other non-nearest voltage vector choices.

Let these vectors be designated as  $S_{XYZ}$  and  $S_{LMN}$ , respectively. These vectors complete the vector triangle desired to reach the output voltage vector at each time instant. The 35 vector parallelogram corresponding to the choices are shown in FIGS. 18-20 using dashed arrows. A correspondence between the nearest switch vector choices and the three voltage waveforms may be established by examining FIG. 17b. For example, at the instant t<sub>x</sub>, second-phase (e.g., 40 B-phase) voltage curve 1708 is the highest and first-phase (e.g., A-phase) voltage curve 1706 is the lowest, while third-phase (e.g., C-phase) voltage curve 1710 is in between. Correspondingly, the choices of vectors in this sector, S<sub>011</sub> and  $S_{010}$ , leads to second top switch 204 of second halfbridge 232 selected to be on throughout the modulation interval, first bottom switch 202 of first half-bridge 230 selected to be on throughout the modulation interval, while third half-bridge 234 is selected to alternate between third top switch 208 on and third bottom switch 210 on.

Each of the six switch vectors can be defined. FIG. 21a shows the switch vector selection  $S_{011}$  connected to link capacitor 110, FIG. 21b shows the switch vector selection  $S_{110}$  connected to link capacitor 110, and FIG. 21c shows the switch vector selection  $S_{101}$  connected to link capacitor 110. Since  $S_{100}$  connected to link capacitor 110, and FIG. 22c shows the switch vector selection  $S_{100}$  connected to link capacitor 110, and FIG. 22c shows the switch vector selection  $S_{001}$  connected to link capacitor 110. Of course, a fewer or a greater number of switch vectors may be defined for a fewer or a greater number of phases.

For example, at the instar be 101 leads to  $\alpha = B$ , phas nected phase, since the other together to the top throw. Since  $S_{001}$  makes  $S_{001$

As another example, at the instant  $t_{\nu}$ , third-phase voltage curve 1710 is the highest and second-phase voltage curve 1708 is the lowest, while first-phase voltage curve 1706 is in 65 between. Correspondingly, the choices of vectors in this sector,  $S_{101}$  and  $S_{001}$ , leads to third top switch 208 of third

18

half-bridge 234 selected to be on throughout the modulation interval, second bottom switch 206 of second half-bridge 232 selected to be on throughout the modulation interval, while first half-bridge 230 is selected to alternate between first top switch 200 on and first bottom switch 202 on.

As yet another example, at the instant  $t_z$ , first-phase voltage curve 1706 is the highest and second-phase voltage curve 1708 is the lowest, while third-phase voltage curve 1710 is in between. Correspondingly, the choices of vectors in this sector,  $S_{100}$  and  $S_{101}$ , leads to first top switch 200 of first half-bridge 230 selected to be on throughout the modulation interval, second bottom switch 206 of second half-bridge 232 selected to be on throughout the modulation interval, while third half-bridge 234 is selected to alternate between third top switch 208 on and third bottom switch 210 on.

For an inverter mode of operation, the switch vectors,  $S_{XYZ}$  and  $S_{LMN}$ , may be two discharge vectors or one charge vector and one discharge vector. Similarly, in a rectifier mode of operation, the switch vectors,  $S_{XYZ}$  and  $S_{LMN}$ , may be two charge vectors or one may be a charge vector and the other a discharge vector. The sequence of selecting the switch voltage vectors,  $S_{XYZ}$  and  $S_{LMN}$ , may also vary. The choice of selecting the switch vectors and ordering their sequence may depend on a power factor of the AC subsystem, a duty ratio (may be too small or large), a rate of change of voltage vector, etc.

The equivalent DC current during a first switch vector  $S_{XYZ}$  can be represented by  $I_{cc}$ , which can take values  $I_A$ ,  $I_B$ , or  $I_C$ , depending on the switch combination represented by XYZ. Similarly, the equivalent DC current during a second switch vector  $S_{LMN}$  can be represented by  $I_B$ , which can take values  $I_A$ ,  $I_B$ , or  $I_C$ , depending on the switch combination represented by LMN. Similarly, the equivalent power transferred to or from the three-phase AC system can be designated as  $P_{XYZ}$  and  $P_{LMN}$  for switch vector selection  $S_{XYZ}$  and  $S_{LMN}$ , respectively, and calculated as

$$P_{XYZ} = 2P_{\alpha} + \frac{I_{\alpha}}{I_{\beta}}P_{\beta} \tag{21} \label{eq:21}$$

$$P_{LMN} = 2P_{\beta} + \frac{I_{\beta}}{I_{c}}P_{\alpha}$$

(22)

where  $P_{\alpha}$  and  $P_{\beta}$  are the powers supplied or consumed by the corresponding  $\alpha$  and  $\beta$  phases, respectively. Here,  $\alpha$  refers to a lone dissimilarly connected phase of the three phases XYZ, and  $\beta$  refers to a lone dissimilarly connected phase of the three phases LMN.

For example, at the instant of time  $t_y$ , selection of XYZ to be 101 leads to  $\alpha=B$ , phase B being the dissimilarly connected phase, since the other phases A and C are connected together to the top throw. Similarly, selection of LMN to be 001 makes  $\beta=C$ . Therefore

$$I_{\alpha} = p|I_B| \tag{23}$$

$$I_{\beta} = p |I_C| \tag{24}$$

$$P_{XYZ} = 2P_B + \frac{I_B}{I_C} P_C \tag{25}$$

$$P_{LMN} = 2P_C + \frac{I_C}{I_D}P_B$$

(26)

where p=-1 for charging switch vectors, and p=1 for discharging switch vectors.

Referring to FIG. 23, a circuit diagram of a second power conversion system 100b is shown in accordance with a second illustrative embodiment. Second power conversion 5 system 100b may include first power source system 102a, a second load system 104b, first converter 106a, second converter 106b, conversion controller 108 (not shown in FIG. 23), an inductive filter 2300, and link capacitor 110. Second load system 104b includes a multi-phase AC load with a unity or a non-unity power factor. For illustration, second load system 104b includes a first-phase AC load 2302, a second-phase AC load 2304, and a third-phase AC load 2306.

Inductive filter 2300 is connected between first converter 15 106a and second load system 104b. Inductive filter 2300 includes first inductor 512, second inductor 514, and third inductor 516. First inductor 512 is connected on first-phase line 224 between first half-bridge 230 and first-phase AC load 2302. Second inductor 514 is connected on second-phase line 226 between second half-bridge 232 and second-phase AC load 2304. Third inductor 516 is connected on third-phase line 228 between third half-bridge 234 and third-phase AC load 2306.

As stated previously if DC power source **500** is connected 25 to link capacitor **110** of FIG. **23**,

$$d_C = V_{in} \sqrt{-\frac{2C}{P_{in}T_s}} \ .$$

After an optional idle interval of time, the energy in link capacitor 110 is directed to second load system 104b by sequentially selecting  $S_{XYZ}$  and  $S_{LMN}$ . As before, during 35 these intervals, DC power source 500 is disconnected from link capacitor 110. Depending on the relative location of the current and voltage vectors at the particular instant of time, and the selection of  $S_{XYZ}$  and  $S_{LMN}$ , in the inverter mode of operation, one of the switch vectors,  $S_{XYZ}$  and  $S_{LMN}$ , may 40 lead to charging or discharging link capacitor 110, while the other switch vector always leads to discharging link capacitor 110. The voltage across link capacitor 110 in each of these cases is illustrated in FIGS. 24 and 25, respectively.

For example, in FIG. **24**, a DC charging curve **2400** 45 indicates a charge of link capacitor **110** by DC power source **500** ( $C_{DC}$ ) followed by a first idle interval **2402**. First idle interval **2402** is followed by an AC load charge curve **2404** as defined by selection of first switch vector,  $S_{XYZ}(C_{AC})$ . AC load charge curve **2404** is followed by a second idle interval **2406**. Second idle interval **2406** is followed by an AC load discharge curve **2408** as defined by selection of second switch vector,  $S_{LMN}(D_{AC})$ . AC load discharge curve **2408** is followed by a third idle interval **2410**, which completes a first switching period  $T_s$ . A greater or a fewer number of idle 55 intervals may be included. In an alternative embodiment, AC load charge curve **2404** may be generated before DC charging curve **2400**.

For example, in FIG. 25, a DC charging curve 2500 indicates a charge of link capacitor 110 by DC power source 60 500 ( $C_{DC}$ ) followed by a first idle interval 2502. First idle interval 2502 is followed by a first AC load discharge curve 2504 as defined by selection of first switch vector,  $S_{XYZ}$  ( $D_{AC1}$ ). First AC load discharge curve 2504 is followed by a second idle interval 2506. Second idle interval 2506 is 65 followed by a second AC load discharge curve 2508 as defined by selection of second switch vector,  $S_{LMN}$  ( $D_{AC2}$ ).

Second AC load discharge curve 2508 is followed by a third idle interval 2510, which completes a first switching period  $T_s$ . As power conversion system 100 source and load demands change as a function of time, discharge and charge curves change to satisfy the demands by changing the selected switch vector and interval length for each charge and/or discharge interval. Again, a greater or a fewer number of idle intervals may be included.

In the case illustrated in FIG. 18, at instant  $t_x$ , both the nearest switch vectors  $S_{011}$  and  $S_{010}$  discharge link capacitor 110. In this case, the capacitor voltage may be illustrated by FIG. 25. In the other case illustrated in FIG. 19, at instant  $t_y$ , one of the nearest switch vectors  $S_{101}$  is charging, while the other one is discharging. In this case, the capacitor voltage may be illustrated by FIG. 24 in this case. In yet another case illustrated in FIG. 20, at instant  $t_z$ , both the nearest switch vectors  $S_{100}$  and  $S_{101}$  discharge link capacitor 110. In this case, the capacitor voltage may be illustrated by FIG. 25.

During the inverter mode of operation, the three-phase AC load discharges or charges link capacitor **110** before discharging link capacitor **110**. The current,  $I_{\alpha}$ , can be an equivalent of current  $I_2$  described above. Therefore, an equation for the duty ratio for first switch vector  $\mathbf{S}_{XYZ}$  can be determined based on equations (10) and (19) as:

$$d_{1inv} = \frac{\sqrt{-2CP_{in1}}}{\sqrt{T_s} I_{\alpha}} \left[ 1 - \sqrt{1 + \frac{P_{XYZ}}{P_{in1}}} \right]$$

(27)

where  $I_{\alpha}$  and  $P_{XYZ}$  are positive for the discharge mode and negative for the charge mode.  $P_{XYZ}$  can be substituted into equation (27) using Equation (21) to define the duty ratio as

$$d_{1inv} = \frac{\sqrt{-2CP_{in1}}}{\sqrt{T_5}} \left[ 1 - \sqrt{1 + \frac{2P_\alpha + \frac{I_\alpha}{I_\beta}P_\beta}{P_{in1}}} \right]$$

(28)

The current  $I_{\beta}$  can be an equivalent of current  $I_{3}$  described above. Therefore, an equation for the duty ratio for second switch vector  $S_{LMN}$  can be determined based on equations (11) and (20) as:

$$d_{2inv} = \frac{\sqrt{2CP_{LMN}}}{\sqrt{T_s I_B^2}}$$

(29)

where and  $I_{\beta}$  and  $P_{LMN}$  are positive.  $P_{LMN}$  can be substituted into equation (29) using Equation (22) to define the duty ratio as

$$d_{2inv} = \sqrt{\frac{2C\left[2P_{\beta} + \frac{I_{\beta}}{I_{\alpha}}P_{\alpha}\right]}{T_{s}I_{\beta}^{2}}}$$

(30)

As the three-phase waveforms unfold through rotation of the current and voltage vectors in the space vector plane, first switch vector  $S_{XYZ}$  and second switch vector  $S_{LMN}$  and the duty ratio for each is determined for each high-frequency switching cycle. FIG. **26***a* illustrates the typical waveforms of the duty ratio behavior of the positive and negative throws

of first half-bridge 230, of second half-bridge 232, and of third half-bridge 234 for an entire power frequency period for first-phase waveform 600, second-phase output waveform 602, and third-phase output waveform 604 of a general case of one nearest and another second nearest switch vector. A first duty ratio curve **2600***a* shows a variation in duty ratio of first top switch 200. A second duty ratio curve 2602a shows a variation in duty ratio of first bottom switch 202, which is an inverse of first duty ratio curve 2600a. A third duty ratio curve 2604a shows a variation in duty ratio of second top switch 204. A fourth duty ratio curve 2606a shows a variation in duty ratio of second bottom switch 206, which is an inverse of third duty ratio curve 2604a. A fifth duty ratio curve 2608a shows a variation in duty ratio of third top switch 208. A sixth duty ratio curve 2610a shows 15 a variation in duty ratio of third bottom switch 210, which is an inverse of fifth duty ratio curve 2608a.

FIG. **26**b illustrates another case of typical waveforms of the duty ratio behavior of the positive and negative throws of first half-bridge 230, of second half-bridge 232, and of 20 third half-bridge 234 for an entire power frequency period for first-phase waveform 600, second-phase output waveform 602, and third-phase output waveform 604 of a general case of the nearest switch vectors. A first duty ratio curve **2600***b* shows a variation in duty ratio of first top switch **200**. A second duty ratio curve 2602b shows a variation in duty ratio of first bottom switch 202, which is an inverse of first duty ratio curve 2600b. A third duty ratio curve 2604b shows a variation in duty ratio of second top switch 204. A fourth duty ratio curve 2606b shows a variation in duty ratio of second bottom switch 206, which is an inverse of third duty ratio curve 2604b. A fifth duty ratio curve 2608b shows a variation in duty ratio of third top switch 208. A sixth duty ratio curve 2610b shows a variation in duty ratio of third bottom switch 210, which is an inverse of fifth duty ratio 35 curve **2608**b.

Referring to FIG. 26a and FIG. 26b, one may observe the duty ratio behavior dependence on the approach for choosing the switch vectors. It may be seen that, the duty ratios consist of linear segments in case of an approach that favors 40 the choice of the second and third nearest switch vectors instead of the two nearest vectors. Referring to FIG. 18, when  $V_X$  is aligned too close to  $S_{011}$  choice of  $S_{011}$  could lead to an unreasonable amount of duty ratio for the state  $S_{011}$ , while the complimentary state could have too small of a duty ratio. Such cases may be avoided through appropriate selection of switch vectors. In inverter applications where capacitor voltage may be limited by an upper bound, a choice of two discharge vectors instead of one charge and one discharge vector may be preferable. Similarly, in recti- 50 fier applications where capacitor voltage may be limited to an upper bound, a choice of one charge vector and one discharge vector instead of two charge vectors may be preferable.

Referring to FIG. 27, switching functions are shown to 55 achieve the appropriate switch throws for first switch vector  $S_{XYZ}$  selected as  $S_{100}$ , and second switch vector  $S_{LMN}$  selected as  $S_{001}$ . A first switching function curve 2700 defines a switching function for source control switch 504. A second switching function curve 2702 defines a switching function for first top switch 200. A third switching function curve (not shown) defines a switching function for first bottom switch 202, which is an inverse of the switching function curve 2704 defines a switching function for second top 65 switch 204. A fifth switching function curve (not shown) defines a switching function curve (not shown) defines a switching function switch 206,

22

which is an inverse of the switching function for second top switch 204. A sixth switching function curve 2706 defines a switching function for third top switch 208. A seventh switching function curve (not shown) defines a switching function for third bottom switch 210, which is an inverse of the switching function for third top switch 208.